Silicon Data Acquisition

170 likes | 304 Views

Silicon Data Acquisition. “Don’t Panic” D Adams. Steve Nahn. Old buddy asks…Why is Silicon Different. Easy: More Physics!. How CDF really takes Data. Whole Shebang run by Trigger System Interface (TSI) Trigger Supervisor = Brains Trigger Crosspoint = TS output

Silicon Data Acquisition

E N D

Presentation Transcript

Silicon Data Acquisition “Don’t Panic” D Adams Steve Nahn

Old buddy asks…Why is Silicon Different • Easy: More Physics! Silis on the Beach - S Nahn

How CDF really takes Data • Whole Shebang run by Trigger System Interface (TSI) • Trigger Supervisor = Brains • Trigger Crosspoint = TS output • Return Crosspoint = TS Input • Scalers = Deadtime Accounting • and clocked by CDF Clock • 53 MHz clock aka TeV RF • Only used by Silicon • CDF Clock (132 nS) • Bunch Crossing Clock (396 nS) • Bunch0 (one turn, 20 s) • Abort Gap (3/turn, ~2 s each) • Supposed to be no beam here Silis on the Beach - S Nahn

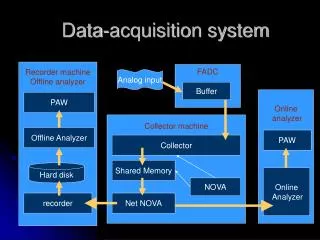

“Normal” DAQ scheme vs. the Silicon Way! • Strip Q sampled every 132 ns • Stored in 46 deep capacitor ring • Silicon reads out “at” L1A • capacitor x marked read only • Q is digitized, capacitor unmarked • ADC VRB buffer and SVT • Why did you do that? • data SVT BEFORE L2 • No separate path for Silicon • After L2A, Data read out of VRB buffer through EVB to L3 • “Tracer Mode” == Post L2A processing • Data sampled @ 132 (396) ns • After L1A, Data 1 of 4 L2 Buffers still in Front End, awaiting L2 Decision • After L2A • Readout by VME CPU • Sent through TRACER to VRBs • Sent from VRBS to L3 via the EVB and REFORMATTED • Note ALL CDF uses VRBs, but not all in the same way • After L3A, data sent to tape and consumers Silis on the Beach - S Nahn

Hardware Involved • Silicon Readout Controller • Source of all Control/Clock • Fiber Interface Board • Translator of SRC commands • Data Manipulator • 104 concentrator • VME Readout Buffer • Bulk Storage for L3 • FIB Fanout/VRB Fanout • Fans in/out from SRC Two SRCs Silis on the Beach - S Nahn

Laundry list of differences • We readout between L1A and L2A in hardware • SRC instead of many tracers • We have two locations of L2 Buffers • In Chip: Taken on L1A, freed after DIGITIZE L1DONE • In VRB: Actually have up to 4 L2 Buffers, 8 Readout Buffers • Our VRBs play an active role in L1 and L2 • We must initialize/control/readout VRBs VRB CPUs • We have the SVX3D ASIC (for better or worse) • Requires initialization rather than just power Handshake • Requires filter between bitsteams in HWDB and editing Silis on the Beach - S Nahn

Some things learned the Hard way: Hardware • FTM Buffing • Poor control signal quality at other end of 71’ cable • Change resistors around on all FTMs: Drive stronger signal • Same time: replace 5 A fuses with 10 A fuses • DOIM Power connections • Bit Errors/“Dropped Readout” from power sag to DOIM Rx • “Gold Pinned” DOIM Rxs swapped in everywhere • Superduper FIBs • “ISL Mod”: stretch out FECLK to avoid ringing (from gangcard) • Applied to SVXII as preventative PRD2/FECLK phase issues • OBDV daughter board: Increase tolerance in OBDV duty cycle • … Silis on the Beach - S Nahn

Some things learned the Hard way: firmware • 2 SRCs is better than one (cf. CDF 6481) • Why wait for L00 (READALL = 15 μs) when it isn’t in the trigger? • VRBs “Early READBUSY” • 2 μs off READOUT time for free • Nibble Shifting • e01209fc 81→ c0e2190 cf18 • FIBs and 00f3: Fibs truncate after n identical bytes • Chips send 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 … • … Silis on the Beach - S Nahn

Dude! What does Run Control code do? • Initialization • Register settings, Chip settings, etc • Either Hardware Database or Calibration Database • Depends on Run type (PHYSICS, CALIBRATION, …) • Diagnostic Readout • Via the Software Event Builder • Monitoring • Low rate publishing of Chip and Board parameters • Undeveloped attempt Occupancy measurement at VRB • Calibration • X-MODE: “Fast” in-crate calibration Silis on the Beach - S Nahn

Why is the software different? • Because the hardware and readout is different • But also, Run Control spec (yes there is one!) emphasizes modularity • Not all things should depend on each other • Leverage work done for teststand into Run Control • Data comes from different place, but actions underneath are the same • Maintain modicum of stability Si software fer Silis on the Beach - S Nahn

Readout rates: Can we go faster? • Speeding up DIGITIZE • “7 bit digitization”: Counting to a lower max ADC value • How low can one go with DPS ON before “00f3” becomes a nightmare • Speeding up READOUT ( == minimizing Occupancy) • Minimize noisy ladder problems • Algorithm with fast turn-around time on optimized thresholds • Nearest Neighbor Sparse • Trouble detecting bit errors – limit to known good ladders? • Better use of available Bandwidth • “Asynchronous Digitize” (aka “Presend Digitize”) • All require some manpower • especially studying effects and monitoring Silis on the Beach - S Nahn

Asynchronous Digitize • If L1A pending, send DIGITIZE process immediately after previous READOUT • Relevant time from “Average longest” to “Longest average” • Requires SRC firmware work and study! Silis on the Beach - S Nahn

Summary? • Silicon DAQ is complicated to get the most physics out of the detector • Is it really complicated? Not if you break it down • Seems a little overdesigned? Well • Most things actually have a good reason for being that way, if you dig deep enough you discover why it is • Various features “we’d never use” have been very handy • Yet, devil is in the details, and the learning curve is not small • Confused, concerned, befuddled? Ask: • Vince’s group at ESE (we owe them lots) • CDF DAQ group (beware their aversion to Silicon) • Your comrades Silis on the Beach - S Nahn

Backup Slides, you Bozo! Silis on the Beach - S Nahn

Changing Chip Parameters • Bitstream is 197 bits x n Chips • Not editable – need a tool to deal with it • Want to change many Chips at once • Incorporate svxdaq Chip interface to allow editing of Hardware database parameters in sane manner • Also incorporate “cloning” tools to apply a single change to pseudo-arbitrary subset of the ~6000 chips. 00000000000000000000000000000000082D36C0062878380E00000000000000000000000000000000A1C5069800050FC70100000000000000000000000000000020B4D80013A0E0E1380000000000000000000000000000000084161B6002143C1C0700000000000000000000000000000080D062034C808287E300000000000000000000000000000000105A6C800950F0701C00000000000000000000000000000000428B0D30010A1E8E030000000000000000000000000000004068B1012640C1C37100000000000000000000000000000000082D36C0042878380E00000000000000000000000000000000A1C5069800050FC70100000000000000000000000000000020B4D80013A0E0E1380000000000000000000000000000000084161B6002143C1C0700000000000000000000000000000080D062034C808287E300000000000000000000000000000000105A6C800950F0701C00000000000000000000000000000000428B0D30010A1E8E030000000000000000000000000000004068B1012640C1C371 Silis on the Beach - S Nahn

“Handshake” between FIB & CAEN crate • Automagic initialization to avoid high current states in the OFF STANDBY transition • Procedure (using Smartsockets) • CAEN CPU broadcasts “I want to turn on SB1W3 All” • FIB crate responds “OK, I can initialize” • CAEN CPU turns on ladder, sees current, and broadcasts “It’s on” • FIB crate responds “OK, I initialized it” • Ladder gets turned off if protocol not followed • Error messsages: • “No response from FIB” • Fib crate or Smartsockets not alive • “did not turn on-tried 10 times” • CAEN CPU never sees current (Immediate Trip, or Interlocked OFF) Silis on the Beach - S Nahn

2 SRC Gains Silis on the Beach - S Nahn