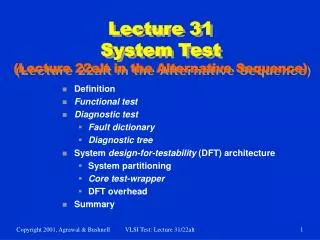

Lecture 31 System Test

Lecture 31 System Test. Definition Functional test Diagnostic test Fault dictionary Diagnostic tree System design-for-testability (DFT) architecture System partitioning Core test-wrapper DFT overhead Summary. A System and Its Testing.

Lecture 31 System Test

E N D

Presentation Transcript

Lecture 31System Test • Definition • Functional test • Diagnostic test • Fault dictionary • Diagnostic tree • System design-for-testability (DFT) architecture • System partitioning • Core test-wrapper • DFT overhead • Summary VLSI Test: Bushnell-Agrawal/Lecture 31

A System and Its Testing • A system is an organization of components (hardware/software parts and subsystems) with capability to perform useful functions. • Functional test verifies integrity of system: • Checks for presence and sanity of subsystems • Checks for system specifications • Executes selected (critical) functions • Diagnostic test isolates faulty part: • For field maintenance isolates lowest replaceable unit (LRU), e.g., a board, disc drive, or I/O subsystem • For shop repair isolates shop replaceable unit (SRU), e.g., a faulty chip on a board • Diagnostic resolution is the number of suspected faulty units identified by test; fewer suspects mean higher resolution VLSI Test: Bushnell-Agrawal/Lecture 31

System Test Applications Application Functional test Diagnostic test Resolution Manufacturing Yes LRU, SRU Maintenance Yes Field repair LRU Shop repair SRU A LRU: Lowest replaceable unit SRU: Shop replaceable unit VLSI Test: Bushnell-Agrawal/Lecture 31

Functional Test • All or selected (critical) operations executed with non-exhaustive data. • Tests are a subset of design verification tests (test-benches). • Software test metrics used: statement, branch and path coverages; provide low (~70%) structural hardware fault coverage. • Examples: • Microprocessor test – all instructions with random data (David, 1998). • Instruction-set fault model – wrong instruction is executed (Thatte and Abraham, IEEETC-1980). VLSI Test: Bushnell-Agrawal/Lecture 31

Gate-Level Diagnosis Karnaugh map (shaded squares are true outputs) Logic circuit b a d T2 T1 b e c a T4 T3 c Stuck-at fault tests: T1 = 010 T2 = 011 T3 = 100 T4 = 110 VLSI Test: Bushnell-Agrawal/Lecture 31

Gate Replacement Fault Karnaugh map (faulty output shown in red) Faulty circuit (OR replaced by AND) b a d T2 T1 b e c a T4 T3 c Stuck-at fault tests: T1 = 010 (pass) T2 = 011 (fail) T3 = 100 (pass) T4 = 110 (fail) VLSI Test: Bushnell-Agrawal/Lecture 31

Bridging Fault Faulty circuit (OR bridge: a, c) Karnaugh map (red squares are faulty outputs) b a+c a d T2 T1 b e c a T4 T3 a+c c Stuck-at fault tests: T1 = 010 (pass) T2 = 011 (pass) T3 = 100 (fail) T4 = 110 (pass) VLSI Test: Bushnell-Agrawal/Lecture 31

Fault Dictionary Fault Test syndrome t1 t2 t3 t4 No fault a0, b0, d0 a1 b1 c0 c1, d1, e1 e0 0 1 0 0 0 0 1 0 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 0 a0 : Line a stuck- at-0 ti = 0, if Ti passes = 1, if Ti fails VLSI Test: Bushnell-Agrawal/Lecture 31

Diagnosis with Dictionary Dictionary look-up with minimum Hamming distance Fault Test syndrome Diagnosis t1 t2 t3 t4 OR AND 0 1 0 1 e0 OR-bridge (a,c) 0 0 1 0 b1 OR NOR 1 1 1 1 c1, d1, e1, e0 VLSI Test: Bushnell-Agrawal/Lecture 31

Diagnostic Tree No fault found T3 b1 T2 c0 OR bridge (a,c) T1 Pass: t4=0 a1 T3 a1, c1, d1, e1 c1, d1, e1 T4 a0, b0, d0 Fail: t4=1 T2 a0, b0, d0, e0 OR AND e0 OR NOR VLSI Test: Bushnell-Agrawal/Lecture 31

System Test: A DFT Problem • Given the changing scenario in VLSI: • Mixed-signal circuits • System-on-a-chip • Multi-chip modules • Intellectual property (IP) cores • Prepare the engineer for designing testable, i.e., manufacturable, VLSI systems. VLSI Test: Bushnell-Agrawal/Lecture 31

Conventional Test:In-Circuit Test (ICT) • A bed-of-nails fixture provides direct access to each chip on the board. • Advantages: Thorough test for devices; good interconnect test. • Limitations: • Works best when analog and digital functions are implemented on separate chips. • Devices must be designed for backdriving protection. • Not applicable to system-on-a-chip (SOC). • Disadvantages: • High cost and inflexibility of test fixture. • System test must check for timing. VLSI Test: Bushnell-Agrawal/Lecture 31

Tested parts In-circuit test (ICT) Easy test access Bulky Slow High assembly cost High reliability Fast interconnects Low cost Untested cores No internal test access Mixed-signal devices PCB vs. SOC PCB SOC VLSI Test: Bushnell-Agrawal/Lecture 31

Core-Based Design • Cores are predesigned and verified but untested blocks: • Soft core (synthesizable RTL) • Firm core (gate-level netlist) • Hard core (non-modifiable layout, often called legacy core) • Core is the intellectual property of vendor (internal details not available to user.) • Core-vendor supplied tests must be applied to embedded cores. VLSI Test: Bushnell-Agrawal/Lecture 31

Partitioning for Test • Partition according to test methodology: • Logic blocks • Memory blocks • Analog blocks • Provide test access: • Boundary scan • Analog test bus • Provide test-wrappers (also called collars) for cores. VLSI Test: Bushnell-Agrawal/Lecture 31

Test-Wrapper for a Core • Test-wrapper (or collar) is the logic added around a core to provide test access to the embedded core. • Test-wrapper provides: • For each core input terminal • A normal mode – Core terminal driven by host chip • An external test mode – Wrapper element observes core input terminal for interconnect test • An internal test mode – Wrapper element controls state of core input terminal for testing the logic inside core • For each core output terminal • A normal mode – Host chip driven by core terminal • An external test mode – Host chip is driven by wrapper element for interconnect test • An internal test mode – Wrapper element observes core outputs for core test VLSI Test: Bushnell-Agrawal/Lecture 31

Wrapper elements Core Functional core inputs Functional core outputs Scan chain Scan chain from/to External Test pins Scan chain to/from TAP A Test-Wrapper Wrapper test controller VLSI Test: Bushnell-Agrawal/Lecture 31

Overhead of Test Access • Test access is non-intrusive. • Hardware is added to each I/O signal of block to be tested. • Access interconnects are mostly local. • Hardware overhead is proportional to: (Block area) – 1/2 VLSI Test: Bushnell-Agrawal/Lecture 31

Overhead Estimate Rent’s rule: For a logic block the number of gates G and the number of terminals t are related by t = K Ga where 1 < K < 5, and a ~ 0.5. Assume that block area A is proportional to G, i.e., t is proportional to A0.5. Since test logic is added to each terminal t, Test logic added to terminals Overhead = ------------------------------------------------- ~ A–0.5 A VLSI Test: Bushnell-Agrawal/Lecture 31

DFT Architecture for SOC Test source Test sink User defined test access mechanism (TAM) Func. outputs Functional outputs Functional inputs Func. inputs Module 1 Module N Test Test wrapper wrapper Instruction register control Test access port (TAP) Serial instruction data TDI SOC outputs TMS TCK TDO SOC inputs TRST VLSI Test: Bushnell-Agrawal/Lecture 31

DFT Components • Test source: Provides test vectors via on-chip LFSR, counter, ROM, or off-chip ATE. • Test sink: Provides output verification using on-chip signature analyzer, or off-chip ATE. • Test access mechanism (TAM): User-defined test data communication structure; carries test signals from source to module, and module to sink; tests module interconnects via test-wrappers; TAM may contain bus, boundary-scan and analog test bus components. • Test controller: Boundary-scan test access port (TAP); receives control signals from outside; serially loads test instructions in test-wrappers. VLSI Test: Bushnell-Agrawal/Lecture 31

Summary • Functional test: verify system hardware, software, function and performance; pass/fail test with limited diagnosis; high (~100%) software coverage metrics; low (~70%) structural fault coverage. • Diagnostic test: High structural coverage; high diagnostic resolution; procedures use fault dictionary or diagnostic tree. • SOC design for testability: • Partition SOC into blocks of logic, memory and analog circuitry, often on architectural boundaries. • Provide external or built-in tests for blocks. • Provide test access via boundary scan and/or analog test bus. • Develop interconnect tests and system functional tests. • Develop diagnostic procedures. VLSI Test: Bushnell-Agrawal/Lecture 31