Evolution in Complexity

460 likes | 602 Views

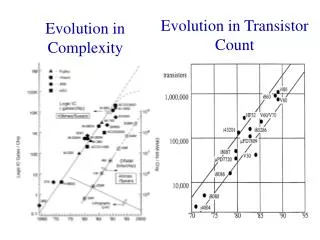

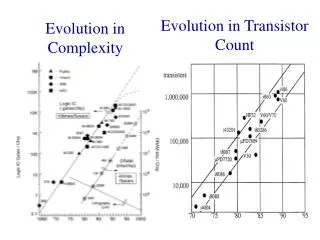

Evolution in Transistor Count. Evolution in Complexity. Evolution in Speed/Performance. Intel 4004 Micro-Processor. Intel Pentium (II) microprocessor. Design Abstraction Levels. Silicon in 2010. Die Area: 2.5x2.5 cm Voltage: 0.6 V Technology: 0.07 m. The Devices. Jan M. Rabaey.

Evolution in Complexity

E N D

Presentation Transcript

Evolution in Transistor Count Evolution in Complexity

Intel 4004 Micro-Processor Intel Pentium (II) microprocessor

Silicon in 2010 Die Area: 2.5x2.5 cm Voltage: 0.6 V Technology: 0.07 m

The Devices Jan M. Rabaey

DIGITAL GATES Fundamental Parameters • Functionality • Reliability, Robustness • Area • Performance • Speed (delay) • Power Consumption • Energy

V DD PMOS Metal1 Polysilicon NMOS CMOS Inverters 1.2 m m =2l Out In GND

4-input NAND Gate Vdd Out GND In1 In2 In3 In4

Building Blocks for Digital Architectures Arithmetic unit Bit-sliced datapath adder - ( , multiplier, shifter, comparator, etc.) Memory - RAM, ROM, Buffers, Shift registers Control - Finite state machine (PLA, random logic.) - Counters Interconnect - Switches - Arbiters - Bus