Introduction

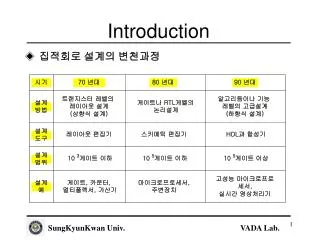

Introduction. 집적회로 설계의 변천과정. Introduction. HDL 설계와 컴퓨터 프로그래밍과의 비교. Introduction. WHAT IS VHDL? VHDL(Very high speed integrated circuit Hardware Description Language) 회로설계에서 상위의 동작 레벨에서부터 하위의 게이트 레벨까지 하드웨어를 기술하고 설계하도록 하는 언어 . CAD 업계 및 IEEE 의 표준 언어 .

Introduction

E N D

Presentation Transcript

Introduction • 집적회로 설계의 변천과정 SungKyunKwan Univ.

Introduction • HDL 설계와 컴퓨터 프로그래밍과의 비교 SungKyunKwan Univ.

Introduction • WHAT IS VHDL? • VHDL(Very high speed integrated circuit Hardware Description Language) • 회로설계에서 상위의 동작 레벨에서부터 하위의 게이트 레벨까지 하드웨어를 기술하고 설계하도록 하는 언어. • CAD 업계 및 IEEE의 표준 언어. • 미국 정부가 지원 및 공인한 하드웨어 설계 언어. • VHDL의 출현 • 하드웨어의 모델링, 문서화, 합성, 검증, 제작 등의 하드웨어 설계 및 관리에서 상당한 불편과 문제점=> 표준화된 HDL이 없었기 때문(VHDL출현의 직접적인 동기) SungKyunKwan Univ.

Introduction • 미국 국방성의 VHSIC(Very High Speed Integrated Circuit) 프로젝트 일부로 만든 것이 VHDL이다. • 1986년 3월부터 시작하여 1987년 12월에 IEEE-1076이라는IEEE 표준 VHDL이 탄생. • 1991년 IEEE-1076에 합성기능의 강화를 위해 9개로 구성된 표준 논리 레벨(‘U’, ‘X’,’0’,’1’,’Z’,’W’,’L’,’H’,’-’)를 정의한 IEEE-1164를 발표. • VHDL을 이용한 회로 설계의 장점 • VHDL을 사용하게 되면 EDA Software나 ASIC Library에 상관없이 설계를 할 수 있다. • VHDL을 이용하여 반도체 내부 회로에 대한 검증부터 System 설계까지 할 수 있다. SungKyunKwan Univ.

Introduction • VHDL로 회로 설계한 것을 Synthesis Software를 이용하여 실제 반도체 회로를 얻을 수 있다. • VHDL의 표현방법 • 동작적 모델링(Behavioral Modeling) • 고급 컴퓨터 언어를 사용해서 프로그램을 작성하는 것과 비슷함. • 시스템의 하드웨어 구조와는 상관없이 표현 • 입력에 따른 출력 결과만을 고려한 기술. • 구조적 모델링(Structural Modeling) • 모든 회로의 컴포넌트(Component) 뿐만 아니라 이들의 상호연결을 나타냄. • Component와 gate와의 상호연결을 나타냄. SungKyunKwan Univ.

Introduction • VHDL을 이용한 설계 과정 SungKyunKwan Univ.

Introduction • Design Entry SungKyunKwan Univ.

Introduction • Function Simulation SungKyunKwan Univ.

Introduction • Synthesis SungKyunKwan Univ.

Introduction • Timing Simulation(Gate-level Simulation) • VHDL을 이용한 방법 • Verilog-HDL을 이용한 방법 • EDIF를 이용하는 방법 SungKyunKwan Univ.

VHDL의 구조 • VHDL의 기본구조 • ENTITY DECLARATION • 설계하고자 하는 회로의 이름과 입출력 인터페이스 정의 • 하드웨어의 검사 및 동작에 필요한 design parameter선언Entity entity_이름 is <generic(generic_list); > <port(port_list);> {선언문} <begin {문장}; >end <entity_이름 >; • Generic • 회로 동작 표현을 위한 design parameter를 선언 • Entity나 ARCHITECTURE에서 사용할 임의의 값을 선언 SungKyunKwan Univ.

VHDL의 구조 • 일단 generic으로 선언된 generic_list는 상수(constant)가 된다 • 회로 표현에 대한 편의성과 공정성을 도모entity sample is generic(B : integer := 3); port(Sel : in std_logic_vector(1 to B); Dout : out std_logic_vector(1 to 2**B);end sample; • Port • 지정어로 시작하며 괄호 안의 port_list를 통하여 외부와 연결 • port_list : mode, data type • data type : std_logic, std_logic_vector, integer 등 • mode : signal의 방향(in, out, inout, buffer) • In : signal이 entity로 들어오는(input)경우에 사용. • Out : entity로부터 나가는(output) 경우 사용. SungKyunKwan Univ.

VHDL의 구조 • Inout : 위의 두 가지 모두가 가능한(bidirectional)경우 사용. • Buffer : out기능에 signal을 entity내에서 다시 읽는 기능을 추가. • 선언문 • 하나의 Entity는 복수개의 Architecture 를 사용할 수 있다. • 이런 여러 종류의 Architecture에서 공용으로 사용할 선언관련 Parameter를 선언해 주는 역할. • 일반적으로 선언문은 Package나 Architecture에서 선언 • Package에서는 공통으로 사용하게 될 선언을 한다 SungKyunKwan Univ.

VHDL의 구조 • 선언문으로 올 수 있는 것 • ALIAS ,ATTRIBUTE, CONSTANT, DISCONNECTION, FILE • SIGNAL, Subprogram 선언 및 동작 표현, SUBTYPE, TYPE, USEentity sample is port(…….); type three_level_logic is (‘0’,’1’,’X’); use WORK.SPECIALS.all; ……end sample; • 문장 • 값의 설정이나 소거와 같은 assertion • Setup/hold time이나 펄스폭 등의 검사(check). • 허용되는 문장 • concurrent assertion문 , concurrent procedure call, process문 SungKyunKwan Univ.

VHDL의 구조 • entity rsff is port(s,r : in std_logic; q,q_bar : buffer std_logic); • constant setup : Time := 10 ns; • begin • ….. • Assert not (s=‘1’ and r=‘1’) <= 조건이 만족하지 않을때 • report “s&r are ‘1’” s와 r이 둘 다 1일 때 • severity ERROR; • ….. • Timingcheck(setup,….); • end; • 최소 entity 선언 • Test bench와 같이 입력과 출력이 없는 하드웨어 구조를 표현. • Entity Test isend; SungKyunKwan Univ.

VHDL의 구조 • ARCHITECTURE BODY • 회로의 실질적인 동작이나 연결 상태 등을 표현 • 하나의 Entity에 복수개의 Architecture사용Architecture architecture_이름 of entity_이름 is {선언문} begin {동작표현}end <architecture_이름 >; • 선언문 • Architecture 안에서 사용할 각종 Type과 변수 종류들을 선언 • 선언문으로 올 수 있는 것 • ALIAS ,ATTRIBUTE, CONSTANT, DISCONNECTION, FILE • SIGNAL, Subprogram 선언 및 동작 표현, SUBTYPE, TYPE, USE SungKyunKwan Univ.

VHDL의 구조 • 동작표현 • 하드웨어의 내부 동작 및 구조를 표현 • 기능에 의한 분류 • Concurrent문 어떤 회로에 대한 동시적인 회로 상태의 변화 표현 문장들의 순서에 상관없이 똑같이 우선순위를 가진다Simulation을 하면 첫번째 줄에 있는 동작 표현이나 마지막 줄에 쓰여진 동작 표현이나 같은 시간에서 동시에 simulation된다. • Sequential문 일반적인 Logic의 순차적 상태를 기술할 수 있는 문자 반드시 앞의 문장이 진행되어야만 뒤의 문장이 실행된다. Concurrent문의 Subprogram과 process문에서만 사용. • 상태에 의한 분류 • Behavioral • Dataflow • Structural SungKyunKwan Univ.

VHDL의 구조 • SUBPROGRAM과 PACKAGE • 많이 사용하거나 중복되는 부분을 function이나 procedure와 같은 subprogram을 이용하여 간단하게 표현. • 이러한 subprogram이나 각종 선언문 등을 따로 모아서 만든 것이 package이다. • Subprogram • Function • 지연 없이 계산하여 return하므로 wait문을 포함할 수 없다. • Signal assignment문을 사용할 수 없다. • Type conversion, 연산자 overloading, signal resolution에 주로 사용. • Parameter는 입력용으로 사용하고 결과 값은 return 뒤에서 정의한 type_지정의 data_type을 가진 function 값을 되돌려 받는다. • Procedure • Signal문과 wait문을 허용. • Parameter를 통하여 입력 값을 전달하고 결과를 받는다. SungKyunKwan Univ.

VHDL의 구조 • Procedure와 function의 형식 • Procedure procedure_이름 <(parameter_list)> is • {선언문} begin {sequential문}end <procedure_이름 >; • Function function_이름 <(parameter_list)> return type_지정 is • {선언문} begin {sequential문}end <function_이름 >; SungKyunKwan Univ.

VHDL의 구조 • Procedure와 function의 예 • Procedure invert1(X : in std_logic; Y : out std_logic) is • begin • if X=‘0’ then • Y <= ‘1’; • else • Y <= ‘0’; • end if; • end invert1; • Function invert2 (X : std_logic) return std_logic is • begin if X=‘0’ then return ‘1’; • else return ‘0’; • end if; • end invert2; SungKyunKwan Univ.

VHDL의 구조 • Package • Data type, function, procedure를 한 장소에 모아서 선언하여 VHDL 설계에서 공동으로 사용할 수 있게 한다. • C 언어에서 header file과 같은 기능. • 독립적인 File로 존재. • Library에 종속되어 다른 VHDL 표현 문장에서 use문 사용하여 참조된다. • Package 형식 • Package declaration • 외부와의 인터페이스 역할.여기에 선언된 것은 외부에서 사용 가능 • VHDL 작성과정에서 공통적으로 필요로 하는 type 선언이나 subprogram 선언을 한다. • Package body package declaration에서 정의한 subprogram의 body포함 SungKyunKwan Univ.

VHDL의 구조 • Package package_이름 is {선언문} end <package_이름 >; • package body package_이름 is • {문장} • end <package_이름 >; • Package declaration 과 body의 사용 예제-- package declaration • Package sample istype three_level_logic is (‘0’,’1’,’X’);function “and”(A,B : three_level_logic) return three_level_logic;end sample; SungKyunKwan Univ.

VHDL의 구조 • -- package body • Package body sample is • function “and” (A,B : three_level_logic) • return three_level_logic is • begin • if A=‘1’ and B=‘1’ then return ‘1’; • elsif A=‘X’ or B=‘X’ then return ‘X’; • else return ‘0’; • end if; end “and”; • -- other subprogram specification • end sample; • Package의 사용 • Use library_이름.package_이름.내용 • Package의 모든 내용을 사용하고 싶을 때는 내용에 all을 사용 SungKyunKwan Univ.

VHDL의 구조 • CONFIGURATION • 하나의 entity에 여러 개의 architecture로 된 design을 simulation할 때 configuration으로 하나의 entity에 하나의 architecture를 연결하여 simulation을 할 수 있다. • Design Unit의 회로 상태를 가장 간단하게 설명 • 계층구조의 회로를 simulation이나 synthesis 할 때 미리 compile된 file의 형태의 데이터 베이스와 연결. • DESIGN LIBRARY • 이미 설계한 것을 저장하여 필요 시에 이용할 수 있도록 설계한 것을 공유하도록 하는 일종의 저장장소(WORKING LIBRARY). • 표준 data type이나 ASCII 파일에서 읽거나 쓰기를 위하여 사용되는 subprogram 등을 정의(RESOURCE LIBRARY). SungKyunKwan Univ.

VHDL의 구조 SungKyunKwan Univ.

VHDL의 구조 • Fig 1. VHDL library and VHDL analyzer • Fig 2. VHDL library and VHDL simulator SungKyunKwan Univ.

VHDL의 구조 • TEST BENCH • Simulation Pattern(Input Stimulus)을 서술하는 문장 • IEEE에 정식 등록 • 다른 Simulator에서도 공동으로 사용 SungKyunKwan Univ.

VHDL의 구조 • 간단한 VHDL 모델링의 예 • 전가산기의 구성 및 진리표 SungKyunKwan Univ.

VHDL의 구조 • 전가산기의 VHDL 모델링 • Entity Declaration • Library ieee; • use ieee.std_logic_1164.all; • use ieee.std_logic_arith.all; • entity Full_Adder is • port ( X,Y,C_in : in std_logic; • S_out,C_out : out std_logic); • end Full_Adder; SungKyunKwan Univ.

VHDL의 구조 • 전가산기의 VHDL 모델링 • Architecture Body(동작적 모델링) • architecture Behave of Full_Adder is • begin • process(X,Y,C_in) • variable l : integer; • begin • l := 0; • if X=‘1’ then l := l+1; end if; • if Y=‘1’ then l := l+1; end if; • if C_in=‘1’ then l:= l+1; end if; • if (l=0) or (l=2) then S_out <= ‘0’; • else S_out <= ‘1’; • end if; • if (l=0) or (l=1) then C_out <= ‘0’; • else C_out <= ‘1’; • end if; • end process; • end Behave; SungKyunKwan Univ.

VHDL의 구조 • 전가산기의 VHDL 모델링 • Architecture Body(구조적 모델링) • architecture Structure of Full_Adder is • signal t_s,t_c1,t_c2 : std_logic • component OR2 • port(i1,i2 : in std_logic; • o : out std_logic); • end component; • component Half_Adder • port(A,B : in std_logic; • S,C : out std_logic); • end component; • begin SungKyunKwan Univ.

VHDL의 구조 • HA1 : Half_Adder • port map (X,Y,t_s,t_c1); • HA2 : Half_Adder • port map (t_s,C_in,S_out,t_c2); • ORG : OR2 • port map (t_c1,t_c2,C_out); • end Structure; SungKyunKwan Univ.

VHDL의 구조 • OR 게이트 VHDL 모델링 • Entity OR2 is • port(i1,i2 : in std_logic; • o : out std_logic); • end OR2; • Architecture Behave of OR2 is • begin • process • begin • if (i1=‘0’) and (i2=‘0’) then • o <= ‘0’; • else • o <= ‘1’; • end if; • wait on i1,i2; • end process; • end Behave; SungKyunKwan Univ.

VHDL의 구조 • 반가산기 VHDL 모델링 • Entity Half_Adder is • port(A,B : in std_logic; • S,C : out std_logic); • end Half_Adder; • Architecture Behave of Half_Adder is • begin • process • begin • if (A=B) then S <= ‘0’; • else S <= ‘1’; • end if; • if (A=‘1’) and (B=‘1’) then C <= ‘1’; • else C <= ‘0’; • end if; • wait on A,B; • end process; • end Behave; SungKyunKwan Univ.

VHDL의 구조 • TEST BENCH • Entity FA_test is • end FA_test; • Architecture Test of FA_test is • signal X,Y : std_logic; • signal C_in : std_logic := 0; • signal S_out,C_out : std_logic; • component Full_Adder • port(X,Y,C_in : in std_logic; • S_out,C_out : out std_logic); • end component; • begin • FA : Full_Adder • port map (X,Y,C_in,S_out,C_out) • X <= ‘0’, • ‘1’ after 40 ns. • ‘0’ after 80 ns; SungKyunKwan Univ.

VHDL의 구조 • Y <= ‘0’, • ‘1’ after 20 ns, • ‘0’ after 40 ns, • ‘1’ after 60 ns, • ‘0’ after 80 ns; • C_in <= ‘0’, • ‘1’ after 10 ns, • ‘0’ after 20 ns, • ‘1’ after 30 ns, • ‘0’ after 40 ns, • ‘1’ after 50 ns; • end Test; • configuration cfg_FA of FA_test is • for Test • for FA : Full_Adder • use entity Work.Full_Adder(Behave); • end for; • end for; • end cfg_FA; SungKyunKwan Univ.

VHDL의 구조 • Simulation 결과 파형 SungKyunKwan Univ.

CONCURRENT문 • 순서에 상관없이 동시 다발적으로 수행되는 문장. • 문장이 위치하는 줄에 상관없이 동시에 수행. • Architecture 본문에서 주로 사용. • BLOCK • PROCESS • PROCEDURE Call • SIGNAL 전달문 • ASSERT • COMPONENT 관련문 • GENERATE SungKyunKwan Univ.

CONCURRENT문 • BLOCK • 회로 설계 시에 내부적으로 계층구조를 가져야 할 때 사용 • Structural표현을 하지 않고 전체 회로 동작을 표현 • [label :] block (guard_조건) • {선언문} • begin • {concurrent문} • end block [label] SungKyunKwan Univ.

CONCURRENT문 • Example1 • entity LATCH is • port ( D, ENB : in std_logic; • Q, QB : out std_logic); • end LATCH; • architecture LATCH_GUARDED of LATCH is • begin • B1 : block (ENB = ‘0’) • begin • Q <= guarded D after 5 ns; • QB <= guarded not (D) after 7 ns; • end block; • end LATCH_GUARDED SungKyunKwan Univ.

CONCURRENT문 • PROCESS • Behavioral로 표현할 수 있는 가장 일반적인 회로 표현 방법 • Sequential문을 본문으로 사용 • [process_레이블 :] • process [(sensitivity_list)] • {선언문} • begin • {sequential문} • end process [process_레이블]; • sensitivity_list : signal의 이름을 list로 가지며 이들 signal중에서 적어도 하나의 값이 변해야 process문이 수행 SungKyunKwan Univ.

CONCURRENT문 • Example • entity AND-OR is • port ( I1,I2 : in std_logic; • O1,O2 : out std_logic); • end AND-OR; • architecture SAMPLE of AND-OR is • begin • process(I1,I2) • begin • O1 <= I1 and I2 after 5 ns; • O2 <= I1 or I2 after 5 ns; • end process; • end AND-OR; SungKyunKwan Univ.

CONCURRENT문 • Example • entity AND-OR is • port ( I1,I2 : in std_logic; • O1,O2 : out std_logic); • end AND-OR; • architecture SAMPLE of AND-OR is • begin • process • begin • O1 <= I1 and I2 after 5 ns; • O2 <= I1 or I2 after 5 ns; • wait on I1, I2; • end process; • end AND-OR; SungKyunKwan Univ.

CONCURRENT문 • SIGNAL 전달문 • Signal로 선언된 선언자나 entity의 port에서 선언된 출력 값에 임의의 상태 값을 전달하는 문장 • 조건적 signal 전달문 • Sequential문의 if와 비슷한 구조 • [label :] signal_이름 <= 파형1 when 조건1 else • 파형2 when 조건2 else • . • . • 파형n-1 when 조건n-1 else • 파형n; SungKyunKwan Univ.

CONCURRENT문 • 선택적 signal 전달문 • Sequential문의 case와 비슷한 구조 • [label :] with 수식 select • signal_이름 <= 파형1 when 선택1, • 파형2 when 선택2, • . • . • 파형n when 선택n; SungKyunKwan Univ.

CONCURRENT문 • Example1(조건적 signal 전달문) • architecture SAMPLE of XOR-GATE is • begin • Z <= ‘0’ after 5 ns when A=B else • ‘1’ after 5 ns; • end SAMPLE; • Example2(선택적 signal 전달문) architecture SAMPLE of DECODER is begin with sel select dout <= “0001” after 5 ns when “00”, “0010” after 5 ns when “01”, “0100” after 5 ns when “10”, “1000” after 5 ns when others; end SAMPLE; SungKyunKwan Univ.

CONCURRENT문 • ASSERT • 임의의 조건에 만족되지 않을 때 내용을 화면에 출력하고 등급을 나누어 Simulation의 진행을 조종 • assert 조건 • [report 메시지] • [severity 레벨] • Report 메시지 • Note : 메시지의 화면 출력 • Warning : 메시지 출력, 발생 시간 및 장소 출력, 시뮬레이션 계속 • Error : 메시지 출력, 시뮬레이션 중지 • Failure : 메시지 출력, 시뮬레이션 상태로부터 빠져 나옴 SungKyunKwan Univ.

CONCURRENT문 • Example • entity RS-FF is • port ( S,R : in std_logic; • Q : out std_logic); • end RS-FF; • architecture SAMPLE of RS-FF is • begin • process • begin • assert not (S=‘1’ and R=‘1’) • report “Both S and R are ‘1’”; • severity Error; • …... • end process • end SAMPLE SungKyunKwan Univ.

CONCURRENT문 • COMPONENT 관련문 • Component Declaration • component식별어 • [generic(….);] • [port(…..);] • end conponent; • Component Instantiation • label : component_이름 • [generic map(association_list);] • [port map(association_list);] SungKyunKwan Univ.

CONCURRENT문 • Example • architecture SAMPLE of TEST is • component sub • port(In1,In2 : in std_logic; • Out1 : out std_logic); • end component; • signal A,B,C ; std_logic; • begin • U0 : sub • port map(In1 => A, In2 => B, Out1 => C); • end TEST; SungKyunKwan Univ.