在典型的编程语言如 C 或 Pascal 中,每个赋值语句按规定的次序,一个接在另一个之后顺序执行,执行的次序由源文件决定。

VHDL 的并行行为. 在典型的编程语言如 C 或 Pascal 中,每个赋值语句按规定的次序,一个接在另一个之后顺序执行,执行的次序由源文件决定。. 在 VHDL 中,结构体的内部没有规定语句的次序,执行的次序仅由对语句中的 敏感信号 发生的事件决定,且语句是同时执行,产生其并行型。. VHDL 的并行行为. ★ 并行赋值语句的一般格式如下:. 信号: 信号名 <= 表达式 变量: 变量名 := 表达式. 作用:将表达式的信号值分配给对象,也就是说每当表达式的信号值变化时执行该语句。.

在典型的编程语言如 C 或 Pascal 中,每个赋值语句按规定的次序,一个接在另一个之后顺序执行,执行的次序由源文件决定。

E N D

Presentation Transcript

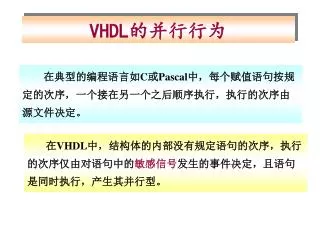

VHDL的并行行为 在典型的编程语言如C或Pascal中,每个赋值语句按规定的次序,一个接在另一个之后顺序执行,执行的次序由源文件决定。 在VHDL中,结构体的内部没有规定语句的次序,执行的次序仅由对语句中的敏感信号发生的事件决定,且语句是同时执行,产生其并行型。

VHDL的并行行为 ★ 并行赋值语句的一般格式如下: 信号: 信号名 <=表达式 变量: 变量名 :=表达式 作用:将表达式的信号值分配给对象,也就是说每当表达式的信号值变化时执行该语句。 注意:每个表达式都至少有一个敏感信号,每当敏感信号改变其值时,赋值语句就执行,

a1 b2 a2 b1 在所有的并行语句中,两个以上的并行赋值语句在字面上的顺序并不表明它们的执行顺序, 例如下面的两个结构体在功能上是等价的。 ENTITY exe ISPORT(a1,a2:IN BIT; b1,b2:OUT BIT);END exe; ARCHITECTURE exe_arc1 OF exe ISBEGIN b1 <= a1 AND b2; b2 <= NOT a1 OR a2;END exe_arc1; ARCHITECTURE exe_arc2 OF exe ISBEGIN b2 <= NOT a1 OR a2;b1 <= a1 AND b2;END exe_arc2;

VHDL的并行行为 ★ 选择信号赋值语句 每一个赋值语句都需要给出一个表达式,同时给出与该表达式的每个可能值相关联的信号 选择信号赋值语句的一般形式如下: WITH < 表达式> SELECT < 对象> <= < 信号1> WHEN < 分支1> , < 信号2> WHEN < 分支2> , < 信号n> WHEN < 分支n> ;

d0 sels d1 d2 out1 d3 s 一个典型的四路数据选择器的VHDL程序说明WITH一般 形式的用法 ENTITY sels IS PORT(d0,d1,d2,d3:IN BIT; s :IN INTEGER RANGE 0 TO 3; out1 :OUT BIT); END sels; ARCHITECTURE sels_arc OF sels IS BEGIN WITH s SELECT out1 <= d0 WHEN 0, d1 WHEN 1, d2 WHEN 2, d3 WHEN 3; END sels_arc;

I0 MUX4 I1 I2 Q I3 A B 例 LIBRARY ieee; USE ieee.std_logic_1164.all;ENTITY mux4 IS PORT(I0,I1,I2,I3,A,B:IN std_logic; Q :OUT std_logic);END mux4; ARCHITECTURE mux4_arc OF mux4 ISSIGNAL sel :INTEGER ;BEGINQ <= I0 AFTER 10 ns WHEN sel= 0 ELSE I1 AFTER 10 ns WHEN sel= 1 ELSE I2 AFTER 10 ns WHEN sel= 2 ELSE I3 AFTER 10 ns ; sel <= 0 WHEN A= ‘0’ AND B= ‘0’ ELSE 1 WHEN A= ‘1’ AND B= ‘0’ ELSE 2 WHEN A= ‘0’ AND B= ‘1’ ELSE 3 ; END mux4_arc;