正反器

正反器. 一、循序邏輯電路. 二、動作情形:用 時序 ( timing ),其次輸出( )是由外界輸入與( )所共同決定。 三、正反器是 雙穩態多諧振盪器 。 四、 1 個正反器可儲存 1 個位元 ,表達 種訊息。 五、 n 個正反器串級可儲存 n 個位元,表達 種訊息。 六、正常情形下,一個正反器有兩個輸出且互為補數。. ▲ 圖 7-1 循序邏輯方塊圖. 正反器基本電路. ▲ 圖 7-2 電晶體雙穩態多諧振盪電路. ▲ 圖 7-3 由 NOT 組成正反器. NAND 閘組成的 RS 正反器.

正反器

E N D

Presentation Transcript

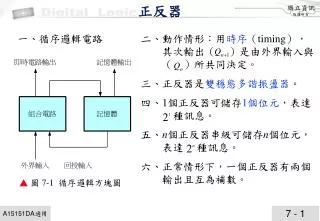

正反器 一、循序邏輯電路 二、動作情形:用時序(timing),其次輸出( )是由外界輸入與( )所共同決定。 三、正反器是雙穩態多諧振盪器。 四、1個正反器可儲存1個位元,表達 種訊息。 五、n個正反器串級可儲存n個位元,表達 種訊息。 六、正常情形下,一個正反器有兩個輸出且互為補數。 ▲ 圖 7-1 循序邏輯方塊圖

正反器基本電路 ▲圖 7-2 電晶體雙穩態多諧振盪電路 ▲ 圖 7-3 由NOT組成正反器

NAND閘組成的RS正反器 ▼表7-1 圖7-4的真值表 ▲圖 7-4 由NAND閘組成的RS正反器

NOR閘組成的RS正反器 ▼表7-3 圖7-5的真值表 ▲圖 7-5 利用NOR閘組成的RS正反器

RS正反器的應用 (b) 未消除彈跳時的接點波形 (a) 電路圖 (c) 消除彈跳後的波形 ▲圖 7-6 RS電閂電路的開關彈跳消除

計時脈波的正緣與負緣 (a) 正邏輯的計時脈波 (b) 負邏輯的計時脈波 ▲圖 7-7 計時脈波的正緣與負緣

時控式RS正反器 ▼表7-5 時控式RS正反器的真值表 ▲ 圖 7-8 時控式RS正反器 (a) 正緣觸發符號 (b) 負緣觸發符號 ▲圖 7-9 時控式RS正反器的符號

RS正反器的特性表、激勵表與布林函數 ▼ 表7-6 時控式RS正反器的特性表 ▼表7-7 時控式RS正反器的激勵表 ▲ 圖 7-10 時控式RS正反器的卡諾圖化簡

時控式D正反器 ▼表7-8 時控式D正反器的真值表 ▲圖 7-11 時控式D正反器的電路圖 ▲ 圖 7-12 時控式D正反器的符號

D型正反器的特性表與激勵表 ▼表7-9 時控式D正反器的特性表 ▼表7-10 時控式D正反器的激勵表 輸出由外界輸入值決定 為記憶體與暫存器的基本電路

時控式JK正反器 ▼表7-11 時控式JK正反器的真值表 ▲圖 7-13 時控式JK正反器的電路圖 ▲圖 7-14 時控式JK正反器的符號

JK正反器的特性表、激勵表與布林函數 ▼表7-12 時控式JK正反器的特性表 ▼表7-13 時控式JK正反器的激勵表 ▲ 圖 7-15 時控式JK正反器的卡諾圖化簡

時控式T型正反器 (b) 符號 (a) 電路圖 ▲圖 7-16 時控式T型正反器的電路圖及符號

時控式T型正反器的真值表、特性表與激勵表 ▼ 表7-16 時控式T型正反器的激勵表 ▼ 表7-14 時控式T型正反器的真值表 ▼表7-15 時控式T型正 反器的特性表 ▲圖 7-17 時控式T型正反器的卡諾圖化簡

主僕式正反器 ▲圖 7-18 主僕式正反器

JK型主僕式正反器 (b) 符號 (a) 實際電路 ▲圖7-19 主僕式正反器

邊緣型觸發正反器 • ▲圖7-20 D型邊緣型觸發正反器

邊緣型觸發正反器的功能表 ▼ 表7-18 正緣觸發(D型FF功能表) ▼表7-17 主僕式觸發(JK型FF功能表)

正反器的預置與清除 • ▲ 圖7-21 正反器的預置與清除

JK正反器替代其他正反器 (a) JK替代異步T型 (b) JK替代同步T型 (c) JK替代D型 ▲圖7-22 JK正反器替代其他正反器

以RS正反器替代其他正反器 • (b) RS替代D型 • (a) RS替代JK型 • (c) RS替代異步T型 • (d) RS替代同步T型 • ▲圖7-23 RS正反器替代其他正反器

以D型正反器替代其他正反器 • (a) D型替代異步T型 • (b) D型替代同步T型 • ▲圖7-24 D型正反器替代其他正反器