Ideas for LLT hardware

Ideas for LLT hardware. Julien Cogan , Régis Lefevre , Patrick Robbe, 10 Apr 2013. Introduction. NEW. OLD. OLD. OLD. OLD. OLD. NEW. Initial LLT architecture: minimal modifications, reusing as much as possible existing hardware.

Ideas for LLT hardware

E N D

Presentation Transcript

Ideas for LLT hardware Julien Cogan, Régis Lefevre, Patrick Robbe, 10 Apr 2013

Introduction NEW OLD OLD OLD OLD OLD NEW Initial LLT architecture: minimal modifications, reusing as much as possible existing hardware. Will show here the changes and improvementsthat are envisagedcompared to this 1st approach

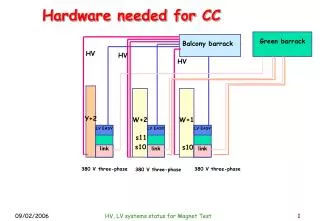

Cyril Drancourt LLT Calo 83 83 36 36 4.8 Gbit/s Getrid of « all » electronics (TVB and 1.6 Gb transmission) thatwereusingalsoold ECS (SPECS) and TFC commands. Optimized option with 3 TRIG40 also possible.

Olivier Duarte LLT Calo • Modifications needed on the FE side (which has to beremade for 40 MHz readout) • Add one extra GBT link (80 bits) for the trigger in addition to the 4 links for DAQ • Format: • 5b local address of Max ET candidate • 16b data for trigger (candidate Max ET and Sum ET) • 12b BXID • 6b of number of calo cellsabove a threshold (to replace SPD multiplicity in LLT) • 5b crate ID (for global address computation), under discussion • 4b FEB ID (for global address computation), under discussion • 1b status • 49/80 bits used • The firmware of the Trigger FPGA (from the old Front-End Board) will have to beslightlymodified, in particular to include the multiplicity computation.

Cyril Drancourt LLT Calo • Implementation on the TRIG40 side • Output (per side): • Hadron candidate • « Electron » candidate • SumET HCAL • SumET ECAL • Multiplicity ECAL • Multiplicity HCAL

Julien Cogan LLT Muon • Scenario for minimal changes on Muon FE side to use GBT to send data: reduce the number of links by 2, readout + trigger would fit in 5 TELL40 thatwould do bothfunctionalities. 4.8 Gbit/s TELL40 TELL40 TELL40 TELL40 TELL40 • Final proposalwillbea slightly more complex variation of thisscheme, depending on the choices for the Muon upgrade.

~6 layers LLTT TRIG40 Tracking VELO LLT accept LLTT tracks (for HLT and monitoring) Giovanni Punzi Low Level Track Triggerintegration LLTT trigger bits VELO • “Copied” from an old muon scheme • Baseline plan is 6 VELO layers - extended plan includes 1-2 UT layers • Important step is to have a detailed status report at the June LLT workshop showing architecture and performance

LLTT connections 8 regions/AMC 2048 Engines/Stratix 12 regions/AMC 3072 Engines/Stratix 12 regions/AMC 3072 Engines/Stratix 12 regions/AMC 3072 Engines/Stratix 12 regions/AMC 3072 Engines/Stratix 12 regions/AMC 3072 Engines/Stratix 12 regions/AMC 3072 Engines/Stratix 12 regions/AMC 3072 Engines/Stratix Giovanni Punzi Might fit inside existing AMCs if not, add up to 6 Tell40 Switch Logic 96 96 96 96 96 96 96 links * 6 layers = 576 links 24*24 links = 576 links = 3links*192 regions … 24 24 24 24 24 … 12 boards in LLTT crate (+SOL40) 256 engines per region = 49152 engines 5 receptors/engine = 245760 receptors 24 AMC =6 TELL40 ATCA backplane 4(?) final decision boards

Slidefrom Federico Alessio « L0DU » AMC board on the S-ODIN ATCA40 boardthatwillimplement the current L0DU functionalities. Firmware to beadaptedfromcurrent L0DU, and communication protocols to bedefined.

Other news • TDR end 2013, commonwithreadoutboard TDR • Emulation of LLT Calo and Muon available in upgrade simulation software (to beupdated to last changes) • Workshop about LLT to beorganized in June to discuss: • Simulation and performance studies • Implementation of the variousfirmwares • Preparation for TDR

Conclusions • Ideas to getrid of old hardware with minimal framework modifications exist for LLT Calo and Muon, and are beingrefined. • Implyheavierprocessing in TRIG40, but possible given the power of theseboards. • Firmwares to bedevelopped for theseboards: • LLT Calo: • LAL Orsay for the trigger part of the Front-End boards • LAPP Annecy for the TRIG40 • LLT Muon: CPPM Marseille • LLT « L0DU »: LPC Clermont • Feasibilitystudies of a tracking LLT subsystem are ongoing (Pisa), fitting in the designed LLT framework.

LLT Muon • Olderpossibility: no change on the Muon Front-End side, move L0Muon computation to TELL40 (TRIG40). TELL40 TELL40 TELL40 TELL40 TELL40 TELL40 TELL40 TELL40 TELL40