Floating point processor for Programmable calculator

Floating point processor for Programmable calculator. Vikas Kumar Sharma Saurabh Gupta Mentors: Veeramani V., Abhinav Agarwal. Outline. IEEE 754 standard Floating Point Arithmetic Addition & Subtraction Multiplication & Division Exceptions Processor Design

Floating point processor for Programmable calculator

E N D

Presentation Transcript

Floating point processor for Programmable calculator Vikas Kumar Sharma Saurabh Gupta Mentors: Veeramani V., Abhinav Agarwal EE Summer Camp 2006

Outline • IEEE 754 standard • Floating Point Arithmetic • Addition & Subtraction • Multiplication & Division • Exceptions • Processor Design • Instruction Set Architecture (ISA) • Processor units • FPGA implementation • Conclusion • Future work • References EE Summer Camp 2006

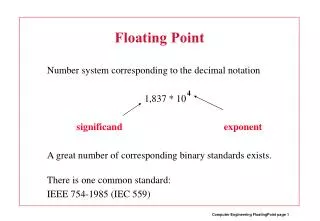

Introduction • Floating point Calculator design • Standard used: IEEE 754 • Operations implemented: - Addition, Subtraction, Multiplication, Division • User programs in hex using simple assembly instructions EE Summer Camp 2006

IEEE 754 standard • Single precision • Sign bit • 0 – Positive • 1 – Negative • Exponent: Biased by 127 • Fraction: implicit ‘1’ excluded from mantissa EE Summer Camp 2006

Zero & Infinity • Zero & Infinity are represented by a special values • 0_00000000_00000000000000000000000 represents 0 and not (1.0)*2^(-127) • 0_11111111_00000000000000000000000 represents ∞ and not (1.0)*2^(128) • Arithmetic needs to be handled separately EE Summer Camp 2006

Arithmetic Algorithms • Addition • Subtraction • Multiplication • Division EE Summer Camp 2006

Addition & Subtraction EE Summer Camp 2006

Multiplication & Division EE Summer Camp 2006

Normalization to IEEE 754 • 0.0000101000000… * 2^(128) • Normalized as 1.010000… * 2^(123) • We need implicit ‘1’ in the IEEE 754 format • How? • Leading Zero Counter • Barrel Shifter • Both these modules are combinatorial EE Summer Camp 2006

Leading Zeros Counter EE Summer Camp 2006

Barrel Shifter EE Summer Camp 2006

Exceptions Behavior • Exceptions Implemented • Out of Bound • Invalid operation • Operation suspended & FPGA LED blink EE Summer Camp 2006

Processor Design – ISA • Register File • 32-bit – IEEE 754 format • 8 registers – sufficient for fairly complex operations • 16-bit Instruction code • Opcode • Destination register address • Source Address 1 • Source Address 2 EE Summer Camp 2006

Instructions • Arithmetic operations – 16 bit, 3 register addresses • Add • Subtract • Multiply • Divide • Move – 48 bit, 1 register address • Termination instruction – 16 bit, all zeros EE Summer Camp 2006

Processor Units EE Summer Camp 2006

Processor Units… • Instruction Fetch Unit (IF) • Starts on reset with counter value zero • Fetches instruction to decoder or register file depending on the instruction type • Instruction Decode Unit (ID) • Starts at the finish of IF • Passes proper ALU unit code to execution module and register addresses to register file EE Summer Camp 2006

Processor Units… • Execution Unit (EX) • Starts at the data read signal from register file • Operands passed to FPU with a activation signal to the required arithmetic unit • Gives the result to Write Back Unit in IEEE 754 format • Write Back Unit (WB) • Starts at the finished execution signal from EX • Selects between the result and the input data depending upon the instruction code EE Summer Camp 2006

Simulation of FPU • Appropriate test benches were used for simulation and design was verified • Exception behavior was checked EE Summer Camp 2006

Simulation of Processor • Expression to calculate (((1.75)/(1.5-1.75))*2.5)+((1.5-1.75)/2.5)= -17.6 • Corresponding instruction set: Move r0, 1.5 Mult r5, r3, r4 Move r1, 1.75 Div r6, r2, r4 Sub r2, r0, r1 Add r7, r5 , r6 Div r3, r1, r2 000000000…00000 Move r4, 2.5 Result by Simulation = -17.60000229 EE Summer Camp 2006

FPGA implementation of FPU EE Summer Camp 2006

FPGA Implementation of processor units EE Summer Camp 2006

Conclusion • FPU unit implemented on FPGA successfully • Complete Processor simulated and synthesized successfully • Optimization required in some parts • Critical issues in synthesis were understood EE Summer Camp 2006

Future work • Double precision • Jump and branch operations • Square Root calculation • Optimization EE Summer Camp 2006

References • Institute of Electrical and Electronics Engineers, ”IEEE Standard for Binary Floating-Point Arithmetic”, ANSI/IEEE Standard 754-1985, August 1985 • http://docs.sun.com/source/806-3568/ncg goldberg.html • http://en.wikipedia.org/wiki/Booth’s multiplication algorithm • http://www.cs.wisc.edu/ smoler/x86text/lect.notes/arith.flpt.html EE Summer Camp 2006

Thank you EE Summer Camp 2006