Optimize Circuit Using Fiduccia-Mattheyses Algorithm

200 likes | 362 Views

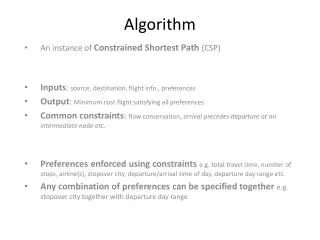

Implement FM algorithm with area constraint [3,5] and alphabetical tie-breaking on a VLSI circuit. Evaluate best solutions, reducing cutsize to 3 with improved balance after certain moves.

Optimize Circuit Using Fiduccia-Mattheyses Algorithm

E N D

Presentation Transcript

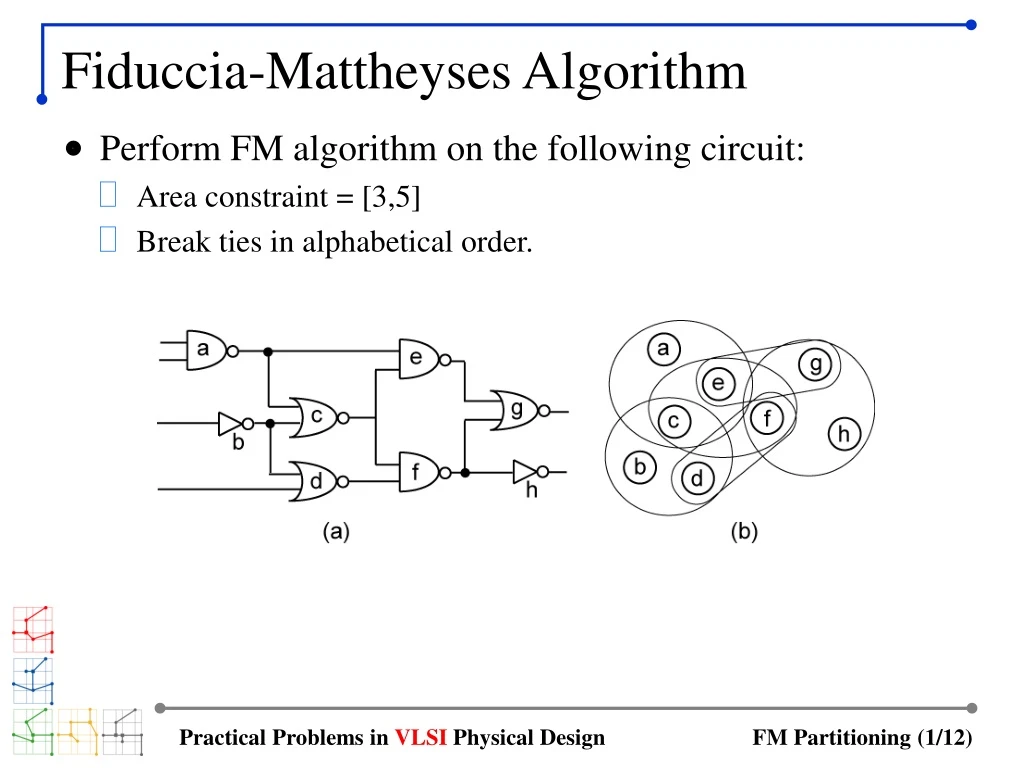

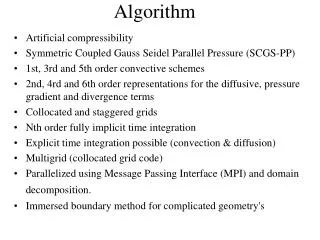

Fiduccia-Mattheyses Algorithm • Perform FM algorithm on the following circuit: • Area constraint = [3,5] • Break ties in alphabetical order. Practical Problems in VLSI Physical Design

Initial Partitioning • Random initial partitioning is given. Practical Problems in VLSI Physical Design

Gain Computation and Bucket Set Up Practical Problems in VLSI Physical Design

First Move Practical Problems in VLSI Physical Design

Second Move Practical Problems in VLSI Physical Design

Third Move Practical Problems in VLSI Physical Design

Forth Move Practical Problems in VLSI Physical Design

Fifth Move Practical Problems in VLSI Physical Design

Sixth Move Practical Problems in VLSI Physical Design

Seventh Move Practical Problems in VLSI Physical Design

Last Move Practical Problems in VLSI Physical Design

Summary • Found three best solutions. • Cutsize reduced from 6 to 3. • Solutions after move 2 and 4 are better balanced. Practical Problems in VLSI Physical Design