Fill the LHC

This document outlines the operational procedures and timing management for the Large Hadron Collider (LHC) beam filling process. It details the role of the Central Timing and the CBCM Sequence Manager in streamlining requests for beam dumps, interfacing with the SPS and TI8/TI2 systems, and managing interlocks. Key use cases include preparing the injector chain, handling beam requests to dumps, and transitioning mastership between systems. The protocols ensure efficient beam delivery while maintaining safety and operational integrity across various sequences.

Fill the LHC

E N D

Presentation Transcript

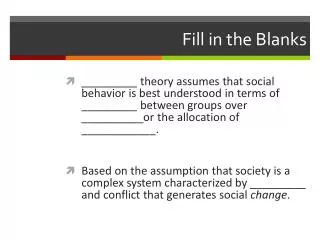

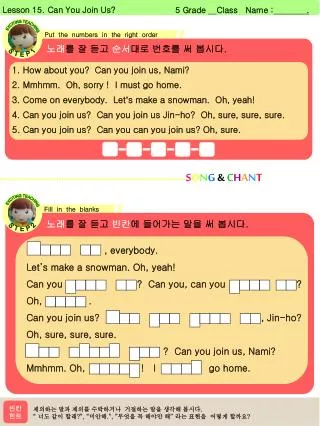

Fill the LHC Central timing use cases

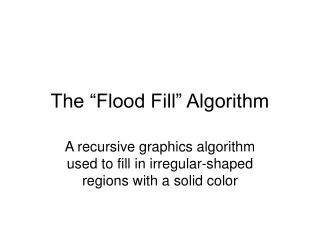

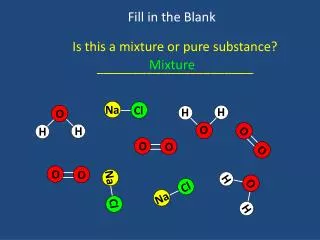

CBCM Sequence Manager LSA Sequencer “LSEQ” CCR TI8/TI2 Dump LHC User Master ON/OFF LHC Fill Requests: Bucket Ring Batches Request TI8/TI2 Dump CS-CCR-CTMGW FESA API LHC Fill Requests: Bucket Ring Batches Reflective Memory Link Request LHC User Normal Spare LIC Sequence LHC Central Timing CBCM Controlling Injector Chain SPS destination request R1,R2 LHC Timing Inhibits Requests Interlocks SIS TI8/TI2 & SPS Dump Inhibits LSEQ Master CPS Batch Request 1,2,3,4 SPS.SPCON.LSEQ SEX.FW1K CTR HIX.FW1K LSEQ changes Allowed LIC Timing

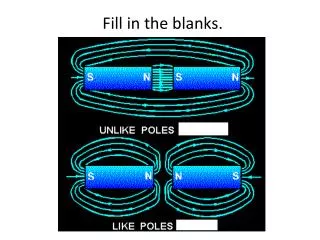

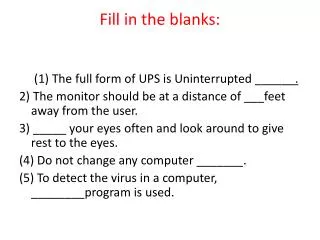

CNGS Default when no LSEQ request and LSEQ is master TI8 Default when no TI8/2 dump and LSEQ is not master Only possible when SIS dump status is “IN” and requested Only possible when LSEQ is master and no TI8/2 SIS inhibits TI8 Dump Default when no batches were requested and LSEQ is master SPS CPS TCLP PSB Linac N.B. When LSEQ is not master all 4 batches hit the SPS dump or the TI8/TI2 dumps. We could send fewer batches if needed… When LSEQ is master, the requested beam could be sent to either LHC… or the TI8/TI2 dump if needed. See Outstanding Issues TI2 Dump SPS Dump D3 Dump TI2

The LHC beam Operators mark the SPS cycle as “TOLHC” Inheritance mechanism propagates “TOLHC” to all cycles in the beam LSEQ Control affects the way “TOLHC” beams are played The SPS telegram contains a new “DYNAMIC” destination calculated on the fly TI8/TI2/TI8_DMP/TI2_DMP/SPS_DMP/CNGS/FT SPS injection plateaux SPS Cycle for the LHC CPS Batch 1 CPS Batch 2 CPS Batch 3 CPS Batch 4 PSB1 PSB1 PSB2 PSB2 PSB3 PSB3 PSB4 PSB4 “TOLHC” The CBCM evaluates LHC beam requests 1.2 seconds before the first PSB cycle in the CBCM time domain. The CBCM time domain is 2.4 seconds ahead of the accelerator complex time domain. Any bad condition will provoke the spare response as usual.

Killing a “TOLHC” CPS batch when it is not requested and LSEQ is the master • The Linac Tail-Clipper timing cuts 99% of the beam at the Linac. • The PSB plays the cycle with no or very little beam. • The CPS destination is forced from the SPS to Dump-3 • The SPS cycle continues as usual, but no CPS beam is injected. • The SPS injection timing for the suppressed batch fires anyway.

Basic behavior • Any abnormal interlock drives the beam into spare. This will result in SPS going in to economy mode. N.B. TI8 dump or TI2 dump are only possible when the dump status (From SIS) indicates that the dumps are in place. • TI8 or TI2 destinations are only possible when LSEQ is master, and when there is a valid LSEQ beam request, and there are no TI8/2 SIS inhibits. • When LSEQ is not the master the default destination is the SPS dump. If a dump in TI8 or TI2 is requested, then the full beam delivered. • When LSEQ is master and there is no request, the beam is killed, but the magnetic cycle takes place. • Mastership can only be changed in the absence of the LHC User request

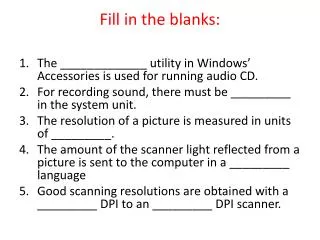

Nominal fill Use case 1Prepare injector chain • LHC operator asks SPS operator to prepare to fill the LHC. • SPS operator removes the SPS LHC cycle request. • If we don’t want to deliver the beam to the SPS dump straight away. • LSEQ mastership must not be changed while the LHC beam is playing !!! • SPS operator loads/runs the LHC fill sequence. • The BCD starts up with LHC beams in spare, and hence the SPS is in economy mode.

Nominal fill Use case 2Beam to TI8/TI2 Dumps • SPS operator want to send the beam to a TI8/TI2 dump • LSEQ is not the master • OP sets the dump targets to move into place and waits (Minutes) • OP selects TI8/TI2 dump request external conditions on central timing. • OP sets LHC user request on. • SIS now should remove inhibits for TI8/2 dump destinations • IF the dump status was bad the LHC beam would be spared, implying that the SPS would go into full economy mode • All CPS batches are now sent to a TI8/TI2 dump

Nominal fill Use case 3Beam to SPS dump • OP want to send the beam to SPS dump. • LSEQ is not the master • The TI8/TI2 Dump requests must be removed. • The LHC User request must be present • All PS batches are now delivered to the SPS dump

Nominal fill Use case 4LSEQ takes mastership • LSEQ now wants to become master. • The LHC user request must be removed. • The current SPS super-cycle will finish and then the LHC beam is spared (= Economy Mode) • The SPS telegram bit SPS.COMLN.LSEQ_ALW gets set by the CBCM. • LSEQ calls the API to request mastership. • If SPS.COMLN.LSEQ_ALW isn’t ready, an error is returned. • LSEQ becomes master, and the LHC user request is turned back on by SPS operations • All beams are played in normal but TCLP, D3 insure there is no beam injected into the SPS. • The SPS destination is SPS dump, and there is no extraction timing.

Nominal fill Use case 5LSEQ Sends beam to LHC • LSEQ wants to send beam to the LHC • LSEQ must be the master • There must be no TI8/2 SIS inhibits. • LHC user request must be asserted • LSEQ makes a request for 1/2/3/4 batches to ring 1/2 bucket N • On the next SPS super cycle the request is executed

Outstanding Issues • How to guarantee the LIC beam is what the LHC expects ? • What are the consequences of padding at the end of the SPS super-cycle ? • Do we need to control the number of CPS batches when not under LSEQ control ? • Do we need to send the beam to TI8/2 dump under LSEQ control ?