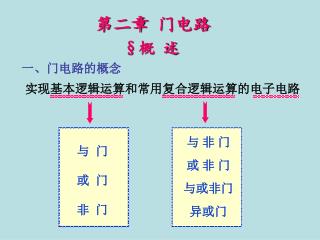

一、门电路的概念

与 非 门. 与 门. 或 非 门. 或 门. 与或非门. 非 门. 异或门. 第二章 门电路. § 概 述. 一、门电路的概念. 实现基本逻辑运算和常用复合逻辑运算的电子电路. 与 非. 与. 或 非. 或. 与或非. 非. 异或. 3V. 3V. 逻辑状态. 二、逻辑变量与两状态开关. 二值逻辑 :. 所有逻辑变量只有两种取值 ( 1 或 0 ). 数字电路中,. 通过电子开关 S 的两种状态 ( 开或关 ) 获得高、低电平,表示 1 或 0. 断开. 1. 高电平 3 V. 低电平. 闭合. 高电平. 0.

一、门电路的概念

E N D

Presentation Transcript

与 非 门 与 门 或 非 门 或 门 与或非门 非 门 异或门 第二章 门电路 §概 述 一、门电路的概念 实现基本逻辑运算和常用复合逻辑运算的电子电路 与 非 与 或 非 或 与或非 非 异或

3V 3V 逻辑状态 二、逻辑变量与两状态开关 二值逻辑: 所有逻辑变量只有两种取值(1 或0) 数字电路中, 通过电子开关S 的两种状态(开或关) 获得高、低电平,表示1 或0 断开 1 高电平 3 V 低电平 闭合 高电平 0 低电平 0 V 电子开关S 可由二极管、三极管或 MOS 管实现

5V 5V 2.4V 2.4V 0.8V 0.8V 0V 0V 三、高、低电平与正、负逻辑 高电平和低电平是两个不同的可以截然区别开来的电压范围。 0 1 0 1 正逻辑 负逻辑 常用

四、分立元件门电路和集成门电路 ①分立元件门电路(目前不使用) 用分立的元器件和导线连接起来构成的门电路。 ②集成门电路 把构成门电路的元器件和连线,都制作在一块半 导体芯片上,再封装起来。 CMOS 集成门电路 常用集成门电路 TTL 集成门电路

五、数字集成电路的集成度 一块芯片中含有等效逻辑门或元器件的个数 小规模集成电路 SSI < 10 门/片 (Small Scale Integration) 或 < 100 元器件/片 中规模集成电路 MSI 10 ~ 99 门/片 (Medium Scale Integration) 或 100 ~ 999 元器件/片 大规模集成电路 LSI 100 ~ 9 999 门/片 或 1 000 ~ 99 999 元器件/片 (Large Scale Integration) 超大规模集成电路 VLSI > 10 000 门/片 计算机中许多芯片就是VLSI,如CPU 或 > 100 000 元器件/片 (Very Large Scale Integration)

S A K 闭合) (断开 断开) (闭合 §2. 1 半导体二极管 、三极管和 MOS 管开关特性 §2. 1. 1 理想开关的开关特性 一、 静态特性 ① 断开 ② 闭合 二、动态特性 ① 开通时间: ② 关断时间: 普通开关:静态特性好,动态特性差 几百万/秒 如继电器、接触器 半导体开关:静态特性较差,动态特性好 几千万/秒 如二极管、三极管及MOS管

/mA 正向 导通区 反向 截止区 P区 N区 - - - - - - - - 0.7 0 0.5 /V + + + + + + + + + - 反向 击穿区 A K §2. 1. 2 半导体二极管的开关特性 一、静态特性 1. 结构示意图、符号和伏安特性 A K 阳极 阴极 PN结 硅二极管伏安特性 ① 外加正向电压(正偏) 二极管导通(相当于开关闭合) ② 外加反向电压(反偏) 二极管截止(相当于开关断开)

D D + + - - 0.7 V + - 2. 二极管的开关作用 [例] 电路如图所示, 试判别二极管的工作 状态及输出电压。 uO = 0 V 二极管截止 [解] uO = 2.3 V 二极管导通

t 0 t 0 二、动态特性 数字电路中,二极管开关工作在高速通断状态。 1. 二极管的电容效应 使二极管的通断需要一段延迟时间才能完成 结电容 Cj 扩散电容 C D 2. 二极管的开关时间 ton — 开通时间 toff — 关断时间 也称反向恢复时间 trr 限制了二极管的开关速度

collector 集电极 N P 基极 N base emitter 发射极 §2. 1. 3 半导体三极管的开关特性 一、静态特性 (电流控制型) (Transistor) 1. 结构、符号和输入、输出特性 (1)结构示意图和符号 c iB iC 集电结 b 发射结 e NPN

iB/ µA uBE/V 0 iC/ mA 4 3 2 1 50 µA 40µA 30 µA 20 µA 10 µA iB = 0 uCE/V 0 2 4 6 8 状态 电流关系 条 件 发射结正偏 放大 iC= iB (2)输入特性 集电结反偏 i C< iB 饱和 两个结正偏 ICS= IBS 临界 iB ≈ 0, iC ≈ 0 截止 两个结反偏 (3) 输出特性 饱 和 区 放大区 数字电路中的三极管作为开关元件,主要工作在饱和和截止两种开关状态,放大区只是极短暂的过渡状态。 截止区

+VCC(12V) Rc 2 k iC + uo Rb + iB T 3V 2.3 k uI -2V 2. 半导体三极管的开关应用 发射结反偏 T 截止 发射结正偏 T 导通 放大还是饱和?

+VCC +12V Rc 2 k iC + uo Rb + iB T 3V 2.3 k uI -2V ≤ 饱和导通条件: 因为 所以

3 t 0 -2 0.9ICS 0.1ICS t 0 3 0.3 t 0 几十ns 二、动态特性 三极管饱和程度↑ ↑

§2. 1. 4 MOS 管的开关特性 MOS(Mental – Oxide – Semiconductor) 金属–氧化物–半导体场效应管FET 一、 静态特性 (电压控制型) 1. 结构和特性 (1) N 沟道 漏极D 集电极 C 类比 栅极 G 基极 B B NPN 衬 底 源极S 发射极 E ★N 沟道增强型MOS管类比于 NPN 型三极管: 1→饱和导通 0→截止

(2) P 沟道 P 沟道增强型 MOS 管与 N 沟道有对偶关系。 漏极D 集电极 C 类比 基极 B 栅极 G PNP B 衬 底 发射极 E 源极S ★P 沟道增强型MOS管类比于 PNP 型三极管: 0 →饱和导通 1 →截止

+VDD +VDD +VDD +10V +10V +10V RD RD RD RD 20 k 20 k 20 k uO D uO uO D D uI uI B G RON uI G S G S S 2. MOS管的开关作用 (1) N 沟道增强型 MOS 管 iD 开启电压 UTN = 2 V

-VDD -VDD -VDD -10V -10V -10V RD RD RD 20 k 20 k 20 k uO uO uO D D D uI uI B uI G G S S G S (2) P 沟道增强型 MOS 管 iD 开启电压 UTP = - 2 V

二、动态特性 1. MOS 管极间电容 栅源电容 CGS 1 ~ 3 pF 栅漏电容 C GD 漏源电容 C DS 0.1 ~ 1 pF 在数字电路中,这些电容的充、放电过程会制约 MOS 管的动态特性,即开关速度。

VDD t 0 0.9ID 0.1ID t 0 VDD t 0 2. 开关时间 开通时间 关断时间

+VCC +10V R0 D1 uA 0 V 0 V 0 V 3 V 3 V 3 V 3 V 0 V uY D2 uB A & Y B §2. 2 分立元器件门电路 ※ § 2. 2. 1 二极管与门和或门 一、二极管与门 电压关系表 真值表 UD = 0.7 V uB/V uA/V uY/V D1 D2 A B Y 导通 导通 0.7 0 0 0 0 0 1 0 0 0 1 1 0 1 1 3V 导通 截止 0.7 0 3 截止 导通 0.7 3 0 0V 导通 导通 3.7 3 3 符号: Y = AB 与门(AND gate)

D1 uA uY D2 uB RO 0 V 0 V 0 V 3 V 3 V 0 V 3 V 3 V -VSS -10V A ≥1 Y B 二、二极管或门※ 电压关系表 真值表 uB/V uY/V uA/V D1 D2 3V A B Y - 0.7 导通 导通 0 0 0 1 1 1 0 0 0 1 1 0 1 1 0V 截止 导通 2.3 0 3 导通 截止 2.3 3 0 UD = 0.7 V 导通 导通 2.3 3 3 Y = A + B 符号: 或门(OR gate)

正逻辑和负逻辑的对应关系: 正与门真值表 负或门真值表 A B Y A B Y 0 0 0 1 1 1 1 0 0 0 0 1 1 0 1 1 1 1 1 0 0 1 0 0 等同 即: 正与门 负或门 等同 正或门 负与门

+VCC +5V iC Rc 1 k iB + Rb T + uO 4.3 k β= 30 uI - - §2. 2. 2 三极管非门(反相器) 一、半导体三极管非门 T 截止 T导通 因为 所以 T 饱和

+VCC +5V iC Rc 1 k iB + Rb T + uO 4.3 k β= 30 uI - - 1 A Y 三极管非门: 真值表 电压关系表 A Y uI/V uO/V Y 0 1 0 5 A 1 0 5 0.3 符号 函数式

+VDD +10V RD 1. 20 k 2. uO D B G uI S + uDS - + uGS - 二、MOS 三极管非门※(类比于NPN型三极管) MOS管截止 MOS 管导通 真值表 A Y 0 1 故 1 0

§2. 3 CMOS 集成门电路 【补充】 • MOS门电路:以MOS管作为开关元件构成的门电路 • CMOS管: MOS管有NMOS管和PMOS管两种。当NMOS管和PMOS管成对出现在电路中,且二者在工作中互补,称为CMOS管(意为互补)。 • CMOS门电路具有制造工艺简单、集成度高、抗干扰能力强、功耗低、价格便宜等优点,发展迅速。 • MOS管有增强型和耗尽型两种。在数字电路中,多采用增强型。

- +VDD uGSP + +10V TP S2 +VDD +VDD G2 B2 +10V +10V D2 RONP TP TP S uA uY D1 uY uY B1 0V 10V G1 S1 TN +10V TN TN RONN S VSS + 1 uGSN A Y - 0V §2. 3. 1 CMOS 反相器 一、电路组成及工作原理 UTN = 2 V UTP = - 2 V uGSN uGSP TN TP uY uA < UTN < UTP 10 V 截止 导通 0 V > UTN > UTP 导通 截止 10 V 0 V

uO /V +VDD TP S2 G2 B2 D2 + uI - uO D1 0 uI /V B1 G1 S1 TN VSS 二、静态特性 1. 电压传输特性: A B VDD C iD UNL UNH D E F UTH UTP UTN 转折(阀值)电压 DE、EF 段: 噪声容限: 指u0为规定值时,允许uI波动的最大范围 uI < UTN , TN 截止、TP 导通, AB 段: CD 段: TN、TP 均导通。 BC 段: TN 导通,uO 略下降。 与BC、AB 段对应,TN、TP 的状态与之相反。 输入为低电平时的噪声容限 UNL: = 0.3VDD uO = VDD 、 iD 0, 功耗极小。 输入为高电平时的噪声容限 UNH: 故CMOS电路采用高电源电压

A B VDD uO / V +VDD C TP S2 UNL UNH G2 B2 D D2 E F + uI - uO UTH D1 UTP UTN 0 uI / V B1 G1 iD / mA S1 TN C D VSS A B E F uI / V 0 2. 电流传输特性: 电压传输特性 iD CD 段: TN、Tp 均导通,流过两管的漏极电流达到最大值 iD = iD(max)。 阈值电压: 电流传输特性 AB、EF 段: TN、TP总有一个为 截止状态,故 iD 0 。 UTH = 0.5 VDD (VDD = 3 ~ 18 V) UTH

& +VDD +10V T Y T P2 P1 uY A T N1 uA B T N2 uB V SS A Y = B §2. 3. 2 CMOS 与非门、或非门、与门和或门 一、CMOS 与非门 TP1与TP2并联 TN1与TN2串联 • 当A、B只要有0V, TN1与TN2 总有一截止,TP1与TP2总有一 导通,Y为10V。 AB Y TN1 TP1 TN2 TP2 1 0 0 截 通 截 通 1 0 1 截 通 通 截 • 当A、B同时为10V,TN1与TN2 都导通,TP1与TP2都截止, Y为0V。 1 0 通 截 截 通 1 1 1 通 截 通 截 0 与非门

+VDD +10V A AB Y TN1 TP1 TN2 TP2 uA 1 0 0 截 通 截 通 B T T P2 P1 uB 0 0 1 截 通 通 截 Y T N1 1 0 通 截 截 通 0 uY 1 1 通 截 通 截 0 T N2 V SS A ≥1 B 二、CMOS 或非门 TP1与TP2 串联 TN1与TN2并联 • 当A、B只要有10V, TN1与TN2 总有一导通,TP1与TP2总有一 截止,Y为0V。 • 当A、B同时为0V,TN1与TN2 都截止,TP1与TP2都导通, Y为10V。 或非门

& A 1 & Y Y B T T P2 P1 +VDD T +VDD N1 TP S2 Y G2 T B2 N2 D2 V A SS A D1 B1 G1 A S1 B TN B VSS 三、CMOS 与门和或门※ 1. CMOS 与门

1 Y T T P2 P1 +VDD +VDD T N1 A TP S2 G2 B2 T A N2 D2 B D1 V SS B1 A G1 ≥1 Y S1 TN A B ≥1 VSS Y B 2. CMOS 或门

1 A & ≥1 Y B C & & & D §2. 3. 3 CMOS 与或非门和异或门 ※ 一、CMOS 与或非门 1. 电路组成 A B 由CMOS 基本电路(与非门和反相器)组成。 Y C D 2. 工作原理

A =1 & & & & Y B 二、CMOS 异或门 1. 电路组成 A 由CMOS 基本电路(与非门)组成。 Y B 2. 工作原理

+VDD u / u u / u TP I O O I TG u / u u / u TN I O O I C VSS C §2. 3. 4 CMOS 传输门、三态门和漏极开路门 ★ 一、 CMOS传输门 (TG 门 — Transmission Gate) 1. 电路组成及符号: (双向模拟开关) 关断电阻大 ( ≥ 109 ) 导通电阻小(几百欧姆) 2. 工作原理: TN、TP均导通, ① TN、TP均截止, ②

+VDD 1 0 A 1 Y T T P1 P2 EN A Y T N2 1 Y A T EN EN N1 0 1 1 V SS 二、CMOS 三态门 1. 电路组成 2. 工作原理 TP2、TN2 均截止 ① Y 与上、下都断开 Y = Z(高阻态 — 非 1 非 0) TP2、TN2 均导通 ② (1 或 0) 3. 逻辑符号 1 0 或 使能端 控制端低电平有效 控制端高电平有效

Y D 1 A Y & B G S B TN C Y & VSS D & 三、CMOS 漏极开路门 (OD门—Open Drain) +VDD 1. 电路组成 外接 RD +VDD RD P1 符号 A B P2 Y 2. 主要特点 ① 漏极开路,工作时必须外接电源和上拉电阻。 ② 可以实现线与功能: 输出端用导线连接起来实现与运算。 ③可实现逻辑电平变换: ④带负载能力强。

§2. 3. 5 CMOS 电路使用中应注意的几个问题(略) 一、CC4000 和C000 系列集成电路 1. CC4000 系列: 符合国家标准,电源电压为 3 18 V,功能和外部引线排列与对应序号的国外产品相同。 2. C000 系列: 早期集成电路,电源电压为 7 15 V,外部引线排列顺序与 CC4000 不同,用时需查阅有关手册。 二、高速 CMOS (HCMOS) 集成电路 54/74 HC(带缓冲输出) 标准门 = 100 ns 传输延迟时间 tpd HCMOS: 54/74 系列 54/74 HCT(与 LSTTL 兼容) HCMOS = 9ns 54/74 BCU(与 LSTTL 兼容)

≥ 三、CMOS 集成电路的主要特点 ① 功耗极低。 LSI:几个 μW , MSI:100 μW ② 电源电压范围宽。 CC4000 系列: VDD = 3 ~ 18 V ③ 抗干扰能力强。 输入端噪声容限 = 0.3VDD ~ 0.45VDD ④ 逻辑摆幅大。 ⑤输入阻抗极高。 ⑥扇出能力强。 扇出系数:带同类门电路的个数,其大小 反映了门电路的带负载能力。 CC4000系列:≥ 50个 ⑦集成度很高,温度稳定性好。 ⑧抗辐射能力强。 ⑨成本低。

四、CMOS电路使用中应注意的几个问题★ 1. 注意输入端的静电防护 2. 注意输入电路的过流保护 3. 注意电源电压极性 4. 输出端不能和电源、地短接 ★ 5. 多余的输入端不应悬空 ★ 与门/与非门:接电源 或与其它输入端并联 多余输入端 如何处理? 或门/ 或非门:接地 或与其它输入端并联 6. 输入端外接电阻的大小不会引起输入电平的变化 ★ 因为输入阻抗极高 (≥ 108 ) 思考原因? 故 输入电流 0,电阻上的压降 0

+VCC(5V) R4 R1 R2 130 4k 1.6k T3 A T2 D Y T1 uI uo D1 T4 R3 1k §2. 4 TTL 集成门电路 (Transistor—Transistor Logic) §2. 4. 1 TTL 反相器 一、电路组成及工作原理 1. 电路组成 D1 — 保护二极管 防止输入电压过低。 当 uI < - 0.5 ~ - 0.7 V 时, 因为 D1 只起保护作用,不参加逻辑判断,为了便于分析,今后在有些电路中将省去。 D1导通, uI被钳制在 - 0.5 ~ - 0.7 V,不可能继续下降。 输入级 中间级 输出级

+VCC(5V) R4 R1 R2 130 4k 1.6k T3 A D T2 T1 Y uI uo T4 R3 1k 2. 工作原理 ① 0.7V 0V 5V 3.6V T1 的基极电压无法使 T2 和 T4的发射结导通 因 T2 、T4 截止 故 T3 、 D 导通

+VCC(5V) R4 R1 R2 130 4k 1.6k T3 A D T2 T1 Y uI uo T4 R3 1k 2. 工作原理 ② 1V T1 倒置放大, (即E极与C极颠倒) 2.1V 4.3V 0.3V iB1流入T2基极 T2 、T4饱和,T3 、D 均截止 1.4V 3.6 V 0.3 0.7V uO = UCES4 ≤ 0.3V 则 所以 uI/V uO/V 0 3.6 3.6 0.3

uO /V +VCC +5V 4 3 1 + - + - 2 uO uI 1 uI /V 0 1 2 3 4 二、静态特性-- 电压传输特性 (1)特性曲线分析: 截止区 A B 线性区 3.6V C 转折区 饱和区 0.3V D E 阈值电压 uB1< 1.3 V, uI < 0.5 V, AB 段: BC 段: uI > 1.4 V, CD 段: DE 段: T2 开始导通(放大区),T4 仍截止。 T2 、T4 截止, T3 、D 导通。 T2 、T4 饱和导通, T3 、D 截止。 反相器的 阈值电压(或 门槛电压) uO = UOL ≤ 0.3 V

1 1 G2 输入低电平时的噪声容限: (2)输入端噪声容限 G2 输入高电平时的噪声容限: uI uO UNH—允许叠加的负向噪声电压的最大值 UNL—允许叠加的正向噪声电压的最大值 G1 G2 输出高电平 输入高电平 典型值 = 3.6 V 典型值 = 3.6 V 输出低电平 输入低电平 典型值 = 0.3 V 典型值 = 0.3 V

uO uI uI t 0 uO t 0 1 三、动态特性(略讲) 传输延迟时间 tPHL— 输出电压由高到 低时的传输延迟 时间。 Uim 50%Uim tPLH— 输出电压由低到 高时的传输延迟 时间。 50%Uom Uom tPHL tPLH tpd — 平均传输延迟时间 典型值: tPHL= 8 ns , tPLH= 12 ns 最大值: tPHL= 15 ns , tPLH= 22 ns

+VCC +5V +VCC +5V b R4 R4 R1 R1 R2 R2 e1 c 130 130 4k 4k 1.6k 1.6k e2 T3 T3 A A T2 T2 D D T1 T1 Y Y B B 3.6V 3.6V 3.6V 3.6V T4 T4 D2 D2 D1 D1 A B Y R3 R3 1k 1k 0 0 0 1 输入级 输入级 中间级 中间级 输出级 输出级 A & 1 0 1 B 1 §2. 4. 2 TTL与非门和其它逻辑门电路 一、TTL 与非门 整理结果: 2. A、B均为 1 1. A、B 只要有一个为 0 T1 — 多发射极三极管 1V 1V 4.3V 4.3V 2.1V 1V 等效电路: 5V 1 理论: 1 1 0.7V 0.7V 0.3V 0.3V 0.3V 3.6V 0 实际: T2 、 T4截止 与非门 T3 、 D导通 T2 、 T4 导通 uO = UCES4 ≤ 0.3V T3 、 D截止

+VCC +5V R4 iB1 1V 2.1V R2 R1 0.3 V 3.6V T3 A T1 D1 D T2 Y 1V 1V R1 i B1 T4 0.3V 0.3 V B R3 T1 A B Y D1 T2 0 0 0 1 A ≥1 1 0 1 B 1 二、TTL 或非门 1. A、B只要有一个为 1 2. A、B均为 0 整理结果: 5V iB1、i B1分别流入T1、T1的发射极 1 0 T2 、 T4 饱和 0.3V 3.6V 0 T2 、 T2均截止 0 T3 、 D截止 则 T4 截止 或非门 uO = 0.3V,Y = 0 输入级 中间级 输出级 T3 、 D导通 其它逻辑门原理相似。