Configuration DataBase

Configuration DataBase. Eric van Herwijnen November 25 th 2003. Contents. Objectives (Where does it fit?) Requirements Detector layout and configuration Users Tools Technology Development plan Conclusions. Experimental Equipment. External data handling architecture (see C. Gaspar).

Configuration DataBase

E N D

Presentation Transcript

Configuration DataBase Eric van Herwijnen November 25th 2003

Contents • Objectives (Where does it fit?) • Requirements • Detector layout and configuration • Users • Tools • Technology • Development plan • Conclusions

Experimental Equipment External data handling architecture (see C. Gaspar)

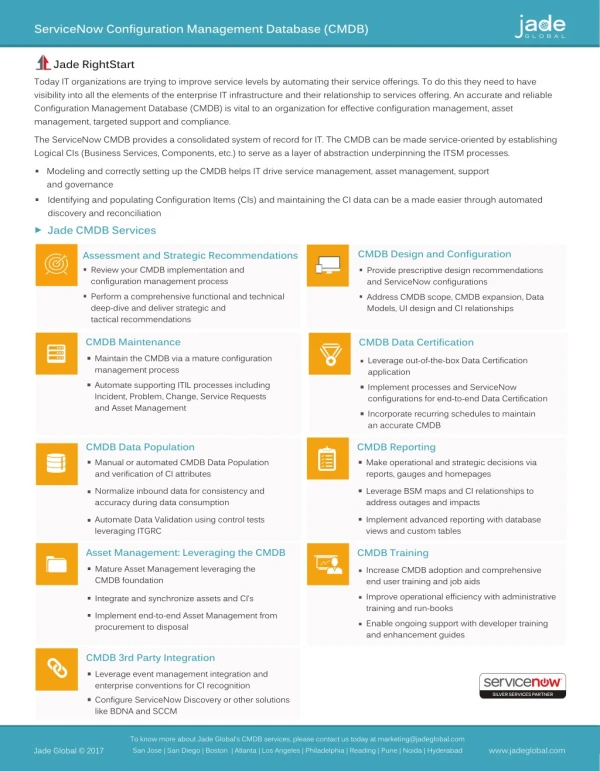

Objectives • Initialize, configure and monitor detector components • e.g. boards, channels, trigger algorithms • Running modes/activities • physics, calibration, subdetector testing • Store configuration data in a database • Design and implementation • Schema • Tools: maintenance, data entry/retrieval, configuration, expansion, navigation

Requirements • Layout • Functions, hierarchy and configuration of components • Logical & physical descriptions • Inventory • Hardware (sensors, control devices, electronics devices) • Where (geographical position) • What it is (serial nb, bar code) • History • Spares • Repairs • Configuration of control system • Bootstrap • Startup of controls pcs in case of failure

Detector layout and configuration • Static information • To startup the detector • Component hierarchy (hw connectivity, network connectivity) • FE electronics (chips, boards); DAQ (network processors, subfarm controllers, pcs); TFC (RU supervisors, switches, throttles); slow control (voltage supplies, CC PCs, VLMCBs); racks, crates • Dynamic information • Activities (cosmics, physics, calibration, debugging) • Detector partitions • Downloadable parameters

Users • Control system • Bootstrap control system • Turn components off/on • Define what to read out • Dynamically build downloadable parameter tables depending on the activity/partition • Configuration db manager • Make large modifications via programs • Others…

Tools • Data retrieval/storage • Which activity, which partition, start run • Extraction tool -> create PVSS project from DB • Cache frequently used recipes • Maintenance • Graphical navigation tool to locate components (in PVSS?) • Version control • Configuration • Partition editor • Expansion • Scripting interface for mass population

Technology • ORACLE for the data base • Java for GUI tools • Python as scripting language • C++ for interfacing to PVSS • IT/CO PVSS configuration DB tool for framework v3.0 will be integrated • Save PVSS configurations in DB • Work done by Z. Maxa • CC PC db with python and xml • Rackwizard & Label bar code java tools • Java tools from CMS (F. Glege)

Development plan • Subdetector data flow, start with TFC • First prototype schema (L. Abadie) • Write some selections in C++ to connect to PVSS • Contact subdetectors for requirements • Second prototype schema (spring 2004) • Design interfaces • Develop tools (spring/summer 2004) • Start adding data (autumn 2004) • First production version early 2005

LODU & L1DU (trigger) • RS (1 running) • TTC encoder(electrical) • L1 trigger derandomiser • Trigger controller(overflow) • Trigger generator(test & calibrations) • Reset & command generator (system problem) • ECS interface • Mode of running (physics,calibration, timing • alignment, test/debug) LHC clock fanout Trigger: overflow • Throttle switch(L0 & L1) • Number of input port:16 • Number of Output port:16 • Output=Logical OR inputs • Resolution=100ns • History>32000 samples(FIFO) • Time-stamp>32 bits • Delay from input to output < 50ns • TFC switch (1) • Input port number:16 • Output port number:16 • I/O: compatible with RD12 TTC • Jitter introduced by switch:<100 ps • Phase ≠ between O ports <100ps • Delay from input to output <10ns TFC Output Throttle Input TFC Dataflow (L. Abadie) • TTCtx (transmitter electr->optical) (16) • 14 outputs + optical couplers (32 outputs) ->448@ • Channel A /B • Throttle OR (L0 & L1) • 32*1 or logical • L1 buffer & L0 • derandomizer->L0 T • L1 derandomizer-> L1 T • L1 FE • TTCrx opti->electr • subdetector name • FE chip • L1 buffer:58254 ev. • L0 FE • TTCrx opti->electr • subdetector name • FE chip detector DAQ

Conclusions • More information at: http://lhcb-comp.web.cern.ch/lhcb-comp/ECS/configurationdb/