Ensuring Correctness of Analog Circuits Using Pattern Matching

180 likes | 357 Views

Ensuring Correctness of Analog Circuits Using Pattern Matching. Rajeev Narayanan , Alaeddine Daghar, Mohamed H. Zaki, and Sofi è ne Tahar Hardware Verification Group, Dept. Of ECE, Concordia University, Montreal, Canada. Motivation. Infinite State Space. Analog Design . Technology

Ensuring Correctness of Analog Circuits Using Pattern Matching

E N D

Presentation Transcript

Ensuring Correctness of Analog Circuits Using Pattern Matching Rajeev Narayanan, Alaeddine Daghar, Mohamed H. Zaki, and Sofiène Tahar Hardware Verification Group, Dept. Of ECE, Concordia University, Montreal, Canada

Motivation Infinite State Space Analog Design Technology Variation Inheritance / Interactive Noise Non-Linearity Combination of traditional and new verification strategies are needed

Outline • Simulation Based Methods • Pattern Matching • Longest Common Subsequence (LCS) • Longest Closest Subsequence (LCSS) • Proposed Methodology • Applications • Colpitts Oscillator • Rambus Ring Oscillator • Conclusion and Future Work

State of the Art - Simulation Behavioral Level Circuit Level Statistical Modeling + Monte-Carlo Simulation • Pros: • Easy to Integrate • Fast • Cons: • Defining Complex Monitors • Accuracy of the Behavioral Model • Pros: • Accurate • Technology Aware • Cons: • Simulation Run-Times • Difficult to Automate

Question? For different Monte-Carlo trials, if the simulation of the non-ideal circuit follows the output of an ideal circuit for say 99.0% and violates just 1.0% of the simulation time, ``Does the designer have to reject the circuit entirely?'' Pattern Matching Algorithm # of Closely Matched Sequence

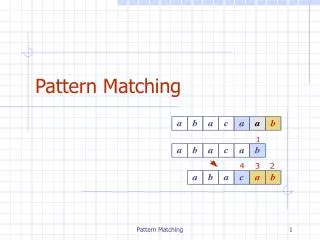

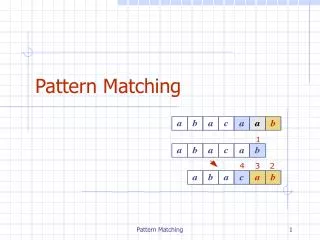

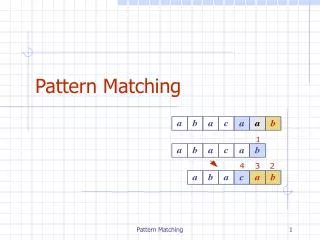

Longest Common Subsequence (LCS) Given two sequences X[1..m] and Y[1..n], find a longest subsequence that is common to X and Y. One-to-One Mapping A B C B D A B B D C A B A Y(1:n) n= 6 X(1:m) m= 7 • One-to-One mapping is NOT possible for Analog Circuits • Closely Matching Sequence for a given tolerance level Longest Closest Subsequence (LCSS) BCBA = LCS(X,Y) Run Time = O(n*2^m)

Longest Closest Subsequence (LCSS) LCSS(X,Y) C[i,j] = C[i-1, j-1] + 1; (X𝑚-p) ≤ Y𝑛 ≤ (X𝑚+p) max{C[i, j-1], C[i-1, j]}; otherwise Recursive Method Brute-Force Method • If 𝑌𝑛 ≤ (𝑋𝑚 +p) and 𝑌𝑛 ≥ (𝑋𝑚 -p), then 𝑍𝑘 is an LCSS of 𝑋𝑚 and 𝑌𝑛 • If 𝑋𝑚 ≠ 𝑌𝑛 , then, if Zk ≠ Xm , then 𝑍𝑘 is an LCSS of 𝑋𝑚-1 and 𝑌𝑛 • If 𝑋𝑚 ≠ 𝑌𝑛 , then, if Zk ≠ Yn , then 𝑍𝑘 is an LCSS of 𝑋𝑚 and 𝑌𝑛-1 Computing the Length of LCSS Optimal Path Finder Worst-Case Run-Time = O(nm)

Example – Chuas Circuit • LCSS perform “Set-by-Set” matching rather than “Value-by-Value” basis (Advantage during Monte Carlo Simulation) • Efficient with offsets and signal with different origins • Matching Percentage: 81.2% • Run-Time Brute-Force: 1.01 sec Recursive: 0.49 sec

Dealing with Offset Conditions • Start-up Delay Time • Drift in Time Axis • Ex: PLL Lock Time • Horizontal Offset • Shift of the entire signal • Ex: Jitter Period Question: How to verify such circuits that have offsets? Or Can we detect these offsets automatically?

Application – Colpitts Oscillator • Voltage divider made by C1 and C2 causes oscillation • L, C1 and C2 determine the frequency of oscillation

LCSS Computational Results • One ideal and Seven different Colpitts Oscillator Circuit • Monte-Carlo Simulation of 1000 trials

Rambus Ring Oscillator Greenstreet et.al, Question: What is the probability that the circuit will have the fastest start-up delay time and what is the “trade-off”? (Needed for PLL!!!)

Parametric Analysis Initial Condition = 1V • Sweep “r” and initial condition • Components Values are fixed at a given time • Not realistic – Follow MonteCarlo Simulation

MonteCarlo Simulation • M = 100 trials

What is the Trade-off? • 38 out of 100 circuits have 67% matching and has fastest start-up delay time (Initial Condition - 1V)

Conclusion and Future Work hvg.ece.concordia.ca • Methodology based on pattern matching for analog circuits • LCSS based on variable simulation step-size • Frequency Offsets • Hypothesis Testing Thank You!