Implication-Based Dynamic Test Set Selection for Efficient On-Chip Diagnosis

This research focuses on using logic implications to create short, specialized test sets for online error detection in semiconductor devices, targeting specific faulty sections for minimal disruption and efficient testing. Experimental setup and results demonstrate the effectiveness of this approach in detecting stuck-at and transition faults, paving the way for future improvements in pinpointing fault locations.

Implication-Based Dynamic Test Set Selection for Efficient On-Chip Diagnosis

E N D

Presentation Transcript

Dynamic Test Set Selection Using Implication-BasedOn-Chip Diagnosis Nicholas Imbriglia, Nuno Alves, Elif Alpaslan, Jennifer Dworak Brown University NATW 2010

Motivation • As electronic devices become smaller, they become more and more susceptible to wearout and latent defects: • Time Dependent Dielectric Breakdown (TDDB) • Negative Bias Temperature Instability (NBTI) • Electromigration

Motivation • This susceptibility is application and workload dependent • Large ramifications for the online testing of homogeneous, multi-core architectures • If a core fails, similar cores should be tested

Our Solution • Efficient online error detection • Detect during normal circuit operation • Efficient online testing of homogeneous cores • Test sets short in length • Focus on a small area of the circuit • Multiple detects in this area

Our Solution • We wish to use the diagnostic information inherent to logic implications to target specific sections of a device • We can then develop test sets specially suited for testing these sections online • These test sets, since they focus only on a portion of the device, can be very short and can be run with minimal interruption of the device’s normal operation

Related Work • Online Error Detection • Triple Modular Redundancy • Berger and Bose Lin Coding • Logic Implications • Online Test • Concurrent Autonomous Chip Self-Test Using Stored Test Patterns (CASP)

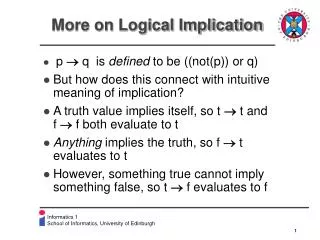

Logic Implications • Provide valuable diagnostic resolution • The checker hardware requires very little knowledge about the circuit’s current state b = 1 f = 0

Logic Implications • Provide valuable diagnostic resolution • The checker hardware requires very little knowledge about the circuit’s current state sa0 sa0 sa1 sa0 sa0 b = 1 f = 0

Generating Pattern Scores • Scores reflect how valuable a pattern is for a given implication • While multiple detections of a fault are useful, we also wish to promote patterns that allow for full coverage of the faults detectable by an implication

Conclusion • We have formulated a procedure for extracting diagnostic information from logic implications • This information was then used to target a specific area of the circuit that is suspected of having an error • Narrowing down the possible locations of an error allowed for the creation of very small, highly specialized test sets

Future Work • Additional work could be done to narrow down the suspected sites even further • A given pattern will only detect a subset of the faults covered by an implication • The results of running patterns could further pinpoint a fault’s location