Advances in Video Signal Processing: Enhanced Shot-Noise Detection and Real-Time Implementation

This paper explores the current status and advancements in video signal processing, focusing on an improved algorithm for shot-noise detection that boasts a 17% enhancement. The implications of this algorithm include better management of mechanical damages and reduced artifacts from block or frame loss. The study highlights refined algorithms suitable for applications in both ASIC and FPGA technologies, maintaining performance without additional area and timing costs. It also discusses successful real-time software implementation on legacy hardware and the development of foundational hardware modules, with future directions for research and lab development outlined.

Advances in Video Signal Processing: Enhanced Shot-Noise Detection and Real-Time Implementation

E N D

Presentation Transcript

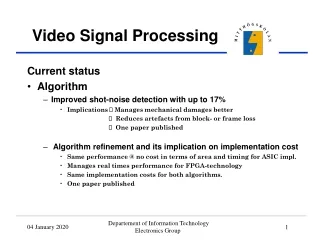

Video Signal Processing Current status • Algorithm • Improved shot-noise detection with up to 17% • Implications Manages mechanical damages better Reduces artefacts from block- or frame loss One paper published • Algorithm refinement and its implication on implementation cost • Same performance @ no cost in terms of area and timing for ASIC impl. • Manages real times performance for FPGA-technology • Same implementation costs for both algorithms. • One paper published Departement of Information Technology Electronics Group

Rapid Hardware Prototyping for Video Signal Processing Håkan Norell Departement of Information Technology Electronics Group

Outline • Video Signal Processing • Real-Time SW • Real-Time HW • Conclusions Departement of Information Technology Electronics Group

Real-time SW • Original algorithm implemented in SW • Aim – Real time performance, Student project. • Results • It is possible to reach real-time performance • Uses MMX technology • Requirements PIII-800 with high-speed disk array • Several benchmark movies and real-world examples has been processed • Environment with I/O interfaces has been developed • Paper in pipeline • Future work • Use the existing model to further refine the algorithm Departement of Information Technology Electronics Group

Real-Time HW • Pre-study of requirements for rapid HW prototyping • Masterthesis • One paper published • Development of low level modules • Physical memory controller interface • Handling of PCI-bus communication • Onboard memory capacity are limited • Need for larger memory • Memory modelling • Benny Thörnberg Departement of Information Technology Electronics Group

Conclusions • Up and running • 3 papers published • Real simulated movies are available • Future directions are visible • Plans to build a Video-Processing Lab Departement of Information Technology Electronics Group