Intermediate Tracker

Intermediate Tracker. Introduction Intermediate trackers/FTD for LC Simulation study Outside Si-tracker option Silicon strip R&D for the intermediate tracker Summary. H. J. Kim, KNU 2004/11/09 7 th ACFA workshop. ▣ Why VTX and tracking important?. • recoil mass reconstruction

Intermediate Tracker

E N D

Presentation Transcript

Intermediate Tracker Introduction Intermediate trackers/FTD for LC Simulation study Outside Si-tracker option Silicon strip R&D for the intermediate tracker Summary H. J. Kim, KNU 2004/11/09 7th ACFA workshop

▣ Why VTX and tracking important? • recoil mass reconstruction - importance of tracking resolution q qbar ( b bbar -> Vertex! )

General view of Three detector option GLD(Huge)

Purpose of Intermediate Tracker *To improve 1) the linking efficiency of a main track to the corresponding VTX hits,2) the reconstruction efficiency of low-momentum tracks and of particles which decay between the VTX and the Main tracking system 3) the momentum resolution of tracks. * If the beam background is very severe, you can turn off the HV of inner layers of TPC without serious performance loss *Trigger and/or Time stamping capability *Standalone tracking

Silicon Tracking for SiD (Jaros’s talk) Why silicon microstrips? SiD starting point Robust against beam halo showers Thin, even for forward tracks. Won’t degrade ECALStable alignment and calibration. No wandering T to D. Excellent momentum resolution (p/p2~2 x 10-5)

TESLA tracking system Magnetic field: 4 Tesla cos(q)=.995 from TESLA TDR

Typical “Large/Huge” models under consideration “Large/Huge” “GLC” design (ACFA) m m SC-coil SC-coil HCAL (Pb(Fe)/scinti or digital) Pb/scinti HCAL W/Scinti ECAL Pb/Scinti ECAL TPC (Jet chamber as option) Jet chamber Si intermedi.-Trk Si intermedi.-Trk SiVTX pixel(cold version) SiVTX pixel

▣ Intermediate Tracker Configuration • stand-alone tracking capability • 5 layers at r = 9 to 37 cm • angular coverage |cosΘ|<0.9 • spatial resolution σ = 10 μm • thickness of a layer: 0.6% Xo Huge detector concept: TPC: Rmin = 40 cm Do not expect much changes in IT

Intermediate Tracker Designfor GLC- Double-sided silicon microstrip detectors i. excellent spatial resolution ii. well-established technologyLayout of the IT surrounding the VTX.- The distance between the last layer of VTX and the first layer of Trackeris about 39cm in Large detector design.i. 5 layers of coaxial cylinders at 9, 16, 23, 30 and 37cmii. covers | |<0.90 coinciding with the region covered by VTX

( ) Momentum Resolution = 10, 20, 30, 40 w/ std. design parameters

CDC IT5 Linking Efficiency Linking efficiency is able to be measured by “Residual” which is defined as a precision from the difference of distance between the position of extrapolate track of main tracking & the hit position on IT or VTX layers Figure. The definition of Residuals.

Residuals for a single pion For a single pion, a linking efficiency with IT+VTX is improved by ~20 % compared to that with VTX only. Residuals vs. generation energy for a single pion

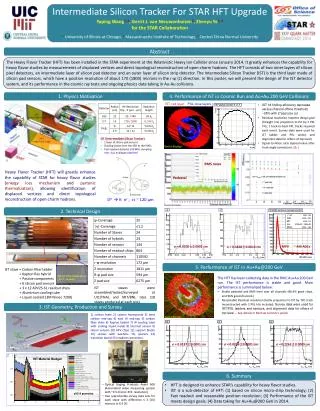

Why Si Tracker ? (Sugimoto’s talk) • 5x10-5 does not satisfy the design criteria if the beam energy spread is 0.1% • The performance goal should be 2x10-5 • How? Outside Si Tracker for a HugeDetector ???

The Detector Model • Si Vertex Detector • 5 layers, t=70mm, s=3mm • cosq < 1 (non-realistic) • Si Inner Tracker • 3 layers (12, 24, 36 cm), t=300mm, s=7mm • cosq <1 (non-realistic) • TPC • 40cm < R < 200cm, Z<235cm • Ar gas, 220 samples, s=150mm • Si Outer Tracker • R=205cm(barrel)/Z=250cm(EC), s=7mm • Momentum resolution is calculated following Gluckstern’s method • No sophisticated method such as Kalman filter is used

Performance DPt/Pt2 Pt (GeV/c)

Performance DP/P2 (M.S. not included) FTD? cosq

n+ ohmic side 1st metal p+ junction side 2nd metal readout line Metal 1 and metal 2 contact (VIA) ▣ Silicon sensor R&D <- Details by B.G.Cheon • • double sided silicon strip • • tree metal process • implant strips in ohmic • side are orthogonal to • those in junction side • readout strips in junction • side have the same • direction as that of ohmic • side Front Side: - brown: implanted n+ - blue: p-stop - sky blue: SiO2 - gray: Al for readout Back Side: - blue: implanted p+ - first gray: 1st metal - sky blue: SiO2 - vertical gray: VIA - second gray: 2nd metal

▣ MASK Design : P Side 64ch 100um pitch sensor 512ch 100um pitch sensor Without hour glass 1cm PIN Diode 16ch 100um pitch sensor 32ch 100um pitch sensor For SDD R&D PIN Diode array 512ch 100um pitch sensor With hour glass 16ch 100um pitch SSD

p+ implanted readout strip n+ implanted readout pad in staggering via in hourglass p-stop in atoll guard ring N side P side ▣Silicon Sensor

▣Measurements of the sensor These are disappeared after insulating wafer edges

RC chip DSSD VA-TA Control Signal FPGA USB2DAQ FADC ▣ Sensor Readout

USB2 with 25Mhz 12bit FADC for Readout R&D FX2 CPLD FADC input trigger 31 FPGA I/O for R&D SRAM Flash RAM

Radiation hardness beamtest with proton • Radiation damage problem • -> Signal reduction • -> Noise increase • -> Depletion voltage increase • -> Sensor damage • Radiation damage Measurement • -> 30-50MeV Cyclotron proton, neutron beam irradiation • (Korean cancer center hospital, Seoul, Korea) • -> Leakage current measurement • -> Capacitance measurement • -> Signal measurement • Processing improvement • -> Radiation damage characteristics study • -> Radiation hardness improvement

IntermediateTracker R&D Activities in Korea √linking and reconstruction efficiency (Fast Simulation) √ track momentum resolution (Full Simulation) √ DSSD simulation/design/fabrication Electronics(RC chip, VA1TA, FADC), DAQ √S/N ratio measurement and beam test Sensor - Kyungpook National University - Korea University - Seoul National University - Chunnam National University - Sungkyunkwan University

Summary • Intermediate Tracker is necessary to improve momentum resolution and track linking efficiency • TPC+Si Tracker System in GLD including SOT will satisfy the original design criteria even for DEb=0.1% in wide angular range (|cosq|<0.9). • Double (single) side silicon strip sensor R&D is ongoing in Korea

Study issue • Intermediate tracker geometry optimization • FTD geometry optimization • Double side vs Single side strip senor • Intermediate tracker trigger? • Time stamping (Separation of bunches) • Radiation hardness • Mechanical structure

▣ MASK Design : N Side 64ch 50um pitch sensor 512ch 50um pitch sensor 32ch 50um pitch sensor 1cm PIN Diode 16ch 50um pitch sensor For SDD R&D PIN Diode array Backside of SSD

▣Intermediate Tracker Option • Require good σrΦ and σz • Reasonable (moderate) cost

DPt/Pt2 : Measurement Term sVTX=3mm in all cases