Reference

Reference. C-S Chang, D-S Lee, and Y-S Jou, “Load Balanced Birkhoff-von Neumann Switches, Part I: One-stage Buffering,” Computer Networks , August 2001. P. S. Sindhu et al . (Juniper Networks), “High Speed Switching Device,” US Patent 5,905,725, May 18, 1999.

Reference

E N D

Presentation Transcript

Reference • C-S Chang, D-S Lee, and Y-S Jou, “Load Balanced Birkhoff-von Neumann Switches, Part I: One-stage Buffering,” Computer Networks, August 2001. • P. S. Sindhu et al. (Juniper Networks), “High Speed Switching Device,” US Patent 5,905,725, May 18, 1999. • P. S. Sindhu et al. (Juniper Networks), “Memory Organization in a Switching Device,” US Patent 6,493,347, Dec 10, 2002.

ULAZNI PORT 0 IZLAZNI PORT 0 M0 ULAZNI PORT 1 IZLAZNI PORT 1 M1 TDM SVIČ TDM SVIČ M2 ULAZNI PORT 2 IZLAZNI PORT 2 M3 ULAZNI PORT N-1 IZLAZNI PORT N-1 KONTROLER Arhitektura BN sviča LUKAP MEMORIJA

M0 M1 ULAZNI PORT N-1 M2 IZLAZNI PORT N-1 M3 KONTROLER LUKAP MEMORIJA Arhitektura BN sviča ULAZNI PORT 0 TDM SVIČ IZLAZNI PORT 0 TDM SVIČ

3-0 3-3 3-3 3-2 3-1 2-2 2-2 2-3 2-0 2-1 1-2 1-1 1-1 1-3 1-0 0-0 0-0 0-1 0-2 0-3 TDM svič • Ulazni moduli su povezani sa memorijskim blokovima preko TDM sviča, a memorijski blokovi su povezani sa izlaznim modulima preko TDM sviča. • U slotu k: spojen ulaz i i izlaz (i+k) mod N.

Algoritam BN sviča • Kada paket stigne, u kontroleru očita se njegova IP adresa, odredi izlazni port i dužina. • Paket se deli na ćelije fiksne dužine. Kontroler zna za svaku ćeliju adresu na kojoj se nalazi, i u kojoj memorijskoj banci. • Kontroler šalje izlaznom sviču zahteve u obliku četvorke (izlazni port, ulazni port, adresa ćelije u memorijskom bloku, memorijski blok) za svaku ćeliju. • Izlazni svič svaki zahtev pošalje odgovarajućem izlazu.

Algoritam BN sviča • Izlazi odvojeno rasporedjuju ćelije prema odredjenom algoritmu koga implementiraju (npr. DRR). • Izlazni popunjavaju tabelu ulaznog sviča zahteva za čitanjem rasporedjenih ćelija iz memorijskih banaka. • Zahtevi za čitanjem se šalju memorijskim bankama kroz ulazni svič.

M0 M1 M2 M3 M4 M5 M6 M7 Tabela za čitanje ćelija • Svako polje u tabeli odgovara jednom vremenskom slotu u budućnosti koji je rezervisan za čitanje iz memorijske banke koja odgovara vrsti tog polja, a od strane izlaza i ako je u polje upisano Bi

Analiza BN sviča • Teorema: Pretpostavimo da paketi dolazi na ulaz i sa verovatnoćom pi, kao Bernulijev proces. Paket je usmeren na izlaz j sa verovatnoćom pij tako da nijedan izlaz nije preopterećen. U ovom slučaju BN svič će propustiti saobraćaj. • Dokaz: Treba pokazati da saobraćaj može da prođe kroz oba TDM sviča, pri tome ni memorijske banke nisu preopterećene upisom i ispisom. Ukupna količina saobraćaja sa ulaza i u memorijsku banku k je: Dakle taj saobraćaj može da prođe kroz svič

Analiza BN sviča Ukupna količina saobraćaja iz memorijske banke k na izlaz j Dakle taj saobraćaj može da prođe kroz svič. Dakle kada paketi dolaze kao Bernuli proces svič je neblokirajući. Da li je ova pretpostavka realna?

Generalizovana analiza blokiranja BN sviča • Teorema: Neka je q(t)=[qij(t)]NxN vektor broja ćelija u redovima za čekanje ulazno-izlaznih parova (i,j) BN sviča. Neka je a(t)=[aij(t)] NxN vektor broja pristiglih paketa ulazno-izlaznih parova (i,j) koji čine stacionaran i slabo korelisan niz slučajnih promenljivih sa srednjom brzinom r(t)=[rij(t)] NxN. Ako je q(0)=0 onda je sistem stabilan, odnosno q(t) konvergira nekoj konačnoj matrici q(∞) ako izlazi nisu preopterećeni:

Generalizovana analiza blokiranja BN sviča • Definicija: Stacionalni proces je onaj čija je statistika nepromenjena u vremenu. Ako sa Өsa(t)=[aij(t+s)] NxN i sa vektor opsega tada kažemo da je proces a(t) stacionaran akko je: • A slabo korelisan akko je:

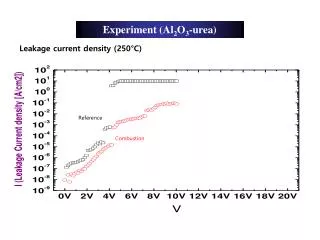

M0 M1 TDM SVIČ M2 M3 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 2 2 2 2 3 2 3 0 2 2 1 1 1 1 1 1 2 2 1 2 2 2 2 2 1 3 2 3 3 3 3 3 3 3 3 3 3 3 3 3 2 Međutim za scenario • Protok pada na 1/N, dakle smanjuje se N puta

Međutim za scenario • U slotu s, ulaz i je povezan sa izlazom k=(i+s) mod N u ulaznom sviču. Pretpostavljamo da na ulaz i dolazi paket za izlaz j =(i+s) mod N. • Dakle, memorijska banka k se napunjena paketima za izlaz k. Ali ova banka je povezana sa ovim izlazom svaki Nti slot, pa prema tome protok ovog izlaza (ili bilo kog drugog izlaza) je najviše 1/N, te je to i protok celog sviča. • Dakle, protok sviča je pao N puta. • Scenario nije nerealan jer se brži tokovi dobijaju od sporijih tokova po RR principu, pa je moguća periodičnost saobraćaja.

Birkoff-von-Neumann(BN) svičevi • Paketi se segmentiraju na ćelije i te se ćelije prosleđuju kroz TDM svič na ulazu, u memorije. • Iz memorija se ćelije čitaju kada dođu na red za opsluživanje, opet kroz TDM svič, sada na izlazu. • Na svakom izlazu se odlučuje o redosledu opsluživanja ćelija, a prema TDM rasporedu. • Prednost je to što nije potreban centralni kontroler. • Mana je što može doći do katastrofalnog blokiranja. • O tome koliko je fer servis nema podataka.

![[Reference]](https://cdn3.slideserve.com/6867974/reference-dt.jpg)

![[Reference]](https://cdn3.slideserve.com/6885011/reference-dt.jpg)

![[Reference]](https://cdn3.slideserve.com/6885026/reference-dt.jpg)