CMOS 集成电路设计基础 - 数字集成电路基础

CMOS 集成电路设计基础 - 数字集成电路基础. 对逻辑门的基本要求. 1 ) 鲁棒性 (用静态或稳态行为来表示) 静态特性常常用电压传输特性( VTC ) 来表示即输出与输入的关系),传输特性上具有一些重要的特征点。 逻辑门的功能会因制造过程的差异而偏离设计的期望值 。. ( 2 ) 噪声容限 :芯片内外的噪声会使电路的响应偏离设计的期望值(电感、电容耦合,电源与地线的噪声)。一个门对于噪声的敏感程度由 噪声容限 表示。. 可靠性―数字集成电路中的噪声.

CMOS 集成电路设计基础 - 数字集成电路基础

E N D

Presentation Transcript

对逻辑门的基本要求 1)鲁棒性(用静态或稳态行为来表示) 静态特性常常用电压传输特性(VTC)来表示即输出与输入的关系),传输特性上具有一些重要的特征点。 逻辑门的功能会因制造过程的差异而偏离设计的期望值。

(2)噪声容限:芯片内外的噪声会使电路的响应偏离设计的期望值(电感、电容耦合,电源与地线的噪声)。一个门对于噪声的敏感程度由噪声容限表示。(2)噪声容限:芯片内外的噪声会使电路的响应偏离设计的期望值(电感、电容耦合,电源与地线的噪声)。一个门对于噪声的敏感程度由噪声容限表示。 可靠性―数字集成电路中的噪声 噪声来源: (1)串扰(2)电源与地线噪声(3)干扰(4)失调应当区分: (1)固定噪声源(2)比例噪声源 浮空节点比由低阻抗电压源驱动的节点更易受干扰 设计时总的噪声容限分配给所预见的噪声源

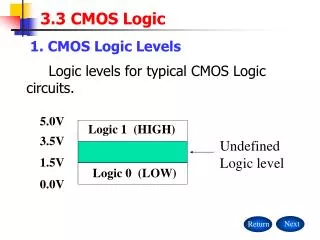

高电平噪声容限 低电平噪声容限

最低输入高电平(VIHmin) 最低输出高电平(VOHmin) 最高输入低电平(VILmax) 最高输出低电平(VOLmax) 高电平噪声容限(NMH) = VOHmin - VIHmin 低电平噪声容限(NML) = VILmax - VOLmax

理想逻辑门 Ri =∞ Ro =0 Fanout =∞ NMH = NML = VDD/2

(3)逻辑门的“单向性”:输出电平的变化不应出现在任何一个输入上但实际情况在输出与输入之间总有反馈。(如密勒效应)(3)逻辑门的“单向性”:输出电平的变化不应出现在任何一个输入上但实际情况在输出与输入之间总有反馈。(如密勒效应) (4)逻辑门的扇出(Fan-out) 和逻辑门的扇入(Fan-in)

(5)逻辑门的面积与复杂性(集成度与速度)(5)逻辑门的面积与复杂性(集成度与速度) (6)动态性能(由动态或瞬态响应来决定) 上升时间、下降时间(tr ,tf ) 传播时间(tPHL ,tPLH ,tP) 一个门的传播时间与扇出和扇入数有关 测量门的延时可以用环型振荡器电路(一般至少五级反相器)实际电路的最高工作频率比环振测得的低50-100倍

(7)逻辑门的功耗 瞬时功耗: p(t) =v(t)i(t) =Vsupplyi(t) 峰值功耗: Ppeak=Vsupplyipeak 平均功耗: 功率延时积 功率延时积(PDP) =E=每操作消耗的能量=Pav×tp 能量延时积 能量延时积(EDP) =门的品质(度量)因子= E×tp

功(热)耗对设计的要求: 功耗影响设计:封装、冷却、电源线尺寸、电源容量、集成度 功耗影响电路的可行性、成本、可靠性。 峰值功耗(确定电源线尺寸)、平均功耗(确定冷却、对电池要求) 动态功耗(翻转功耗)、静态功耗(漏电功耗) 传播延时与功耗的关系:功耗延时积、能量延时积

一阶RC电路的延时 tp =ln (2) τ=0.69 RC 这一模型可以用来模拟反相器延时

MOS开关及CMOS传输门 单管MOS开关 NMOS单管开关 NMOS单管开关电路如图所示, CL为负载电容, UG为栅电压, 设“1”表示UG=UDD, “0”表示UG=0(接地)。 (a) 电路; (b) 等效开关; (c) 传输特性

(1) 当UG=“0”(接地)时, NMOS管截止(开关断开), 输出Uo=0。 (2) 当UG=“1”(UDD)时, NMOS管导通(开关合上), 此时视Ui的大小分两种情况: ① Ui<UG-UTH(UTH为NMOS管阈值电压), 输入端呈开启状态, 设Uo初始值为零, 则Ui刚加上时, 输出端也呈开启状态, NMOS管导通, 沟道电流对负载电容充电, 直至Uo=Ui。

② Ui>UG-UTH, 输入端沟道被夹断, 此时若Uo初始值小于(UG-UTH), 则输出端沟道存在, NMOS管导通, 沟道电流对CL充电, Uo上升。但随着Uo上升, 沟道电流逐渐减小, 当Uo升至(UG-UTH)时, 输出端沟道也被夹断, 导致NMOS管截止, 从而使输出电压Uo维持在(UG-UTH)不变。 若此时Ui=UG=UDD, 则输出电压Uo为 Uo=UG-UTH=Ui-UTH=UDD-UTH

PMOS单管开关 PMOS单管开关电路如图所示, 其衬底接UDD。 (1) 当UG=“1”(接UDD, 高电平)时, PMOS管截止, 开关断开, Uo=0。 (2) 当UG=“0”(接地, 低电平)时, PMOS管导通, 视Ui的大小不同, 也分两种情况: ① Ui=“1”(UDD)时, 输入端沟道开启导通, 电流给CL充电, Uo上升, 输出端沟道也开启, 开关整个接通, 有Uo=Ui=“1” ② Ui=“0”(低电平)时, 输入端沟道被夹断, 此时要维持沟道导通, 则输出端沟道开启, 输出电压Uo必须比UG高一个PMOS管的阈值电压|UTHP|。 因此, 当传输输入为0的信号时, 输出同样存在所谓的“阈值损失”, 即 Uo=|UTHP|

当开关控制电压(UG)使MOS管导通时, NMOS、 PMOS传输信号均存在阈值损失, 只不过NMOS发生在传输高电平时, 而PMOS发生在传输低电平时。 下图给出了阈值损失的波形示意图。

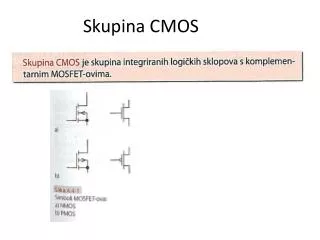

CMOS传输门 根据NMOS和PMOS单管开关的特性, 将其组合在一起形成一个互补的CMOS传输门, 这是一个没有阈值损失的理想开关。 CMOS传输门电路 CMOS传输门电路如图 所示, NMOS管和PMOS管的源极、 漏极接在一起, NMOS衬底接地, PMOS衬底接UDD(保证了沟道与衬底之间有反偏的PN结隔离), 二者的栅极控制电压反相, 即UGP= ~UGN 。

CMOS传输门的直流传输特性 CMOS传输门的直流传输特性如图 所示, 它不存在阈值损失问题: (1) 当UGN=“0”, UGP=“1”时, N管、 P管均截止, Uo=0。 (2) 当UGN=“1”, UGP=“0”时, Ui由“0”升高到“1”的过程分为以下三个阶段(分析中, 设“1”为UDD=5V, “0”为接地(0 V), UTHN=|UTHP|=0.9 V): ① Ui较小, 有 UGN-Ui>UTHN N管导通 |UGP-Ui|<UTHP P管截止 N管导通区 此时, N管接近理想开关, N管沟道电流向CL充电,使Uo=Ui。

② Ui升高, 有 UGN-Ui>UTHN N管导通 |UGP-Ui|>|UTHP| P管导通 双管导通区 此时, N管、 P管共同向CL充电, 仍使Uo=Ui。 ③ Ui再升高, 接近“1”时, 有 UGN-Ui<UTHN N管截止 |UGP-Ui|>|UTHP| P管导通 P管导通区 此时,P管接近理想开关, P管沟道电流向CL充电,使Uo=Ui

CMOS传输门的设计要点 为保证导电沟道与衬底的隔离(PN结反偏), N管的衬底必须接地, P管的衬底必须接电源(UDD)。 沟道电流ID与管子的宽长比(W/L)成正比, 为使传输速度快, 要求ID大些, 沟道长度L取决于硅栅多晶硅条的宽度, 视工艺而定。 一般L取工艺最小宽度(2λ), 那么, 要使ID大, 就要将沟道宽度W设计得大一些。

CMOS 反相器的特点 (一)电压摆幅接近电源电压,噪声容限大。 (二)为无比逻辑 当反相器的阈值在电压摆幅的中点时,高与低电平的噪声余量相同,此时的噪声容限最大

3.1.1 反相器静态特性 随着Ui由小变大(0→UDD), 反相器的工作状态可分为5个阶段来描述。

反相器的直流传输特性 (a) 电路; (b) 直流传输特性

1. AB段 • 在AB段, 0<Ui<UTHN, IDN=0, N管截止, P管非恒流(饱和)导通, 有 • Uo=UOH=UDD • 2. BC段 • UTHN<Ui<Uo+|UTHP| • 即 • UGDP=|Ui-Uo|<|UTHP|

3. CD段 当Ui进一步增大, 且满足 Uo+|UTHP|≤Ui≤Uo+UTHN N管和P管的电流相等, 根据电流方程:

令 则 且 可得反相器的阈值电压UiT为

4. DE段 随着Ui继续上升, 当满足 Uo+UTHN<Ui<UDD+UTHP 时, N管退出恒流(饱和)导通, 进入线性导通区, 而P管仍维持在恒流(饱和)导通区。 N管做为P管的负载管, rdsn很小, 所以增益减小, Uo变化缓慢。 5. EF段 随着Ui进一步增大, 当满足 UDD+UTHP≤Ui≤UDD 时, P管截止, IDP=0, N管维持非饱和导通而导致Uo=0。

CMOS反相器功耗 1. 静态功耗PS 当Ui=0 时,V1截止,V2导通,Uo=UDD(“1”状态)。 当Ui=UDD(“1”)时,V1导通,V2截止,Uo=0(“0”状态)。 因此, 无论Ui是“0”或“1”, 总有一个管子是截止的, ID=0, 故静态功耗 PS=ID×UDD=0

2. 动态功耗(瞬态功耗)PD 1) 对负载电容CL充放电的动态功耗PD1——交流开关功耗 设输入信号Ui为理想方波。 当Ui由“0”→“1”时, 输出电压Uo由“1”→“0”, V1导通, V2截止, IDN使CL放电(反充电), Uo下降。 反之, Ui由“1”→“0”时,输出电压Uo由“0”→“1”, V1截止, V2导通, IDP给CL充电, Uo上升。 因此, 在输入信号变化的一段时间内, 管子存在电流和电压, 故有功率损耗。

一周内CL充放电使管子产生的平均功耗 式中Tc为输入信号周期

Ui为非理想阶跃波形时引入的动态功耗PD2——直流开关功耗Ui为非理想阶跃波形时引入的动态功耗PD2——直流开关功耗

对NMOS管, UGSN=Ui, 则: (1) 当UGSN=Ui<UTHN时,NMOS管截止; (2) 当UGSN=Ui>UTHN时, NMOS导通。 对PMOS管, UGSP=Ui-UDD, 则: (1) 当|UGSP|=|Ui-UDD|<|UTHP|时, PMOS管截止; (2) 当|UGSP|=|Ui-UDD|>|UTHP|时, PMOS管导通。

因此, 在t1~t2, t3~t4时间段内, NMOS管和PMOS管同时导通, iDN=iDP≠0, UDSN、 UDSP也不为0, 产生瞬态功耗PD2, 该电流贯穿NMOS管和PMOS。 设电流峰值为IDM, 其平均电流近似为IDM/2, 那么, 电源供给的平均功率(也就是管子消耗的平均功率)为 式中: tr=t2-t1——Ui的上升时间; tf=t4-t3——Ui的下降时间。

总的反相器功耗 PD=PD1+PD2 由以上分析可得结论: 要降低功耗, 必须要按比例减小管子的尺寸(CL减小), 特别是减小供电电压UDD。

CMOS反相器的门延迟、 级联以及互连线产生的延迟 1. CMOS反相器的延迟分析模型 用于CMOS反相器延迟分析的RC模型如图所示, 将管子导通时的电流电压关系等效为一个电阻, 其中RP表示P管导通时的等效电阻, RN表示N管导通时的等效电阻; RL为连线电阻, CL为负载电容。 如果反相器级联, 那么CL代表下一级反相器的输入栅电容。

CMOS反相器上升时间tr、 下降时间tf、 延迟时间td的计算 1) tr、 tf、 td的定义 tr: 输出电压Uo从0.1UDD上升到0.9UDD所需的时间(UDD为Uo的振幅)。 tf: 输出电压Uo从0.9UDD下降到0.1UDD所需的时间。 td: Uo从0上升到0.5UDD所需的时间。 暂令RL=0, 则CL充放电电路如图所示。

tr、 tf的计算 CL充电期Uo(t)表达式为 CL放电期Uo(t)表达式为 根据tr和tf的定义, 得 tr=2.2RPCL tf=2.2RNCL

反相器延迟时间td的计算 反相器延迟时间分上升延迟时间tdr和下降延迟时间tdf, 总的平均延迟时间td为 延迟时间td的含义