Project Stickleback A CMOS Weekend Countdown Timer

240 likes | 257 Views

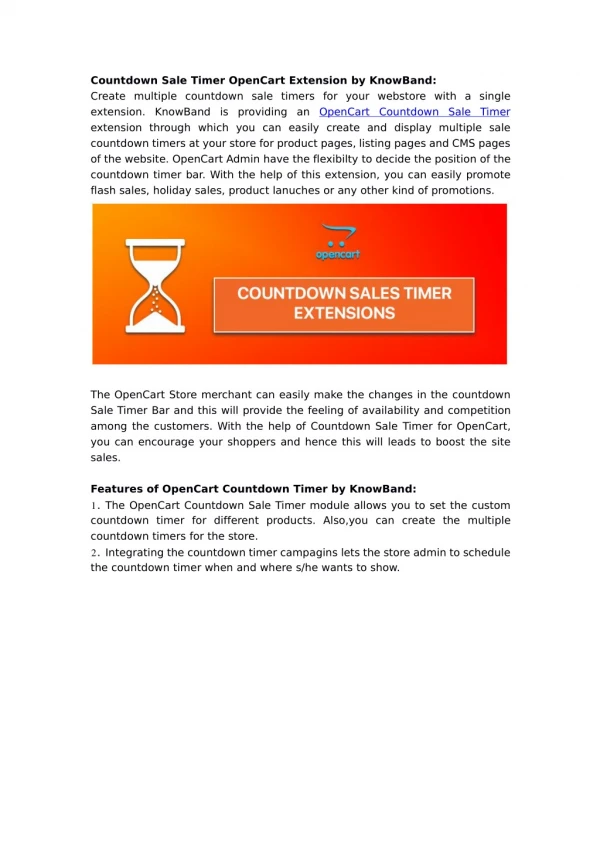

This project introduces Project Stickleback, a CMOS weekend countdown timer, developed by the University of Portland School of Engineering. The timer displays the remaining days, hours, minutes, and seconds left in the workweek and provides a separate message on the weekend. The system was successfully designed, fabricated, and verified, and allows users to easily set the time.

Project Stickleback A CMOS Weekend Countdown Timer

E N D

Presentation Transcript

Project SticklebackA CMOS Weekend Countdown Timer • Advisor • Joseph P. Hoffbeck, Ph.D. • Yuin-Hwa Lu, Ph.D. • Industry Representative • Mr. Chris Vondrachek • Intel Corp. Authors Tony Faris Joe Leineweber Jeff Schlichting University of Portland School of Engineering

Agenda • Introduction Jeff • Background Jeff • Methods Tony • Results Tony • Conclusions Joe • Demonstration Joe University of Portland School of Engineering

Introduction • Thank you’s • Advisors • Dr. Hoffbeck • Dr. Lu • Informal Advisors • Dr. Osterberg • Sandy Ressel • Rick Severs • Industry representative • Chris Vondrachek University of Portland School of Engineering

Introduction • Problem • Determine the amount of time remaining in the workweek • Solution • Project Stickleback – A CMOS Weekend Countdown Timer University of Portland School of Engineering

Introduction • What time does it use? • 9am Monday for the week start • 5pm Friday for the week end • What does it display? • Displays the days, hours, minutes, and seconds left in the work week • Displays a separate message on the weekend University of Portland School of Engineering

Background • Key Features • Visibly display the remaining time in the workweek • Run without supervision • Allow users to easily set the time University of Portland School of Engineering

Methods • Fall 2003 • Hand design • B2Logic simulation • .tpr file • MOSIS fabrication University of Portland School of Engineering

Methods • Spring 2004 • Macromodel – Verilog file • System construction • MOSIS chip replacement and finalization University of Portland School of Engineering

Results University of Portland School of Engineering

Results • MOSIS chip B2Logic simulation University of Portland School of Engineering

Results University of Portland School of Engineering

Results University of Portland School of Engineering

Results • .tpr file University of Portland School of Engineering

Results • MOSIS chip layout University of Portland School of Engineering

Results • Verilog file University of Portland School of Engineering

Results University of Portland School of Engineering

Results University of Portland School of Engineering

Conclusions • System 100% Verified • All Tasks Completed On-Time • All Objectives Were Successfully Met • Designed and fabricated a CMOS chip • Took an idea all the way to a product • Learned how to work in a team environment University of Portland School of Engineering

Demonstration:Setting the Clock University of Portland School of Engineering

Demonstration:Monday Morning University of Portland School of Engineering

Demonstration:Monday Morning University of Portland School of Engineering

Demonstration:Friday Evening University of Portland School of Engineering

Demonstration:Friday Evening University of Portland School of Engineering

Questions? University of Portland School of Engineering