第三章 CPU 子系统

第三章 CPU 子系统. 运算部件. 寄存器. 寄存器. 控制部件. 运算器. 控制器. 第三节 组合逻辑控制器原理. 送 M. 微命令序列. PC. +1. I/O 状态. 控制台信息. 微命令 发生器. …. 译码. 送 M 或 ALU. 地址形成. 运行状态. D. θ. 寻. PSW. 时序. IR. 来自 M. 3.3.1 控制器组成. 送 M. 微命令序列. PC. +1. I/O 状态. 控制台信息. 微命令 发生器. …. 译码. 送 M 或 ALU. 地址形成. 运行状态.

第三章 CPU 子系统

E N D

Presentation Transcript

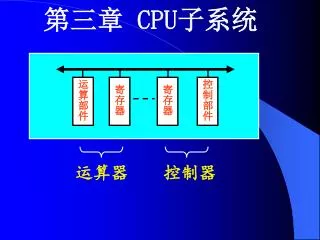

第三章 CPU子系统 运算部件 寄存器 寄存器 控制部件 运算器 控制器

第三节 组合逻辑控制器原理 送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU 地址形成 运行状态 D θ 寻 PSW 时序 IR 来自M 3.3.1 控制器组成

送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU 地址形成 运行状态 微命令 发生器 D θ 寻 PSW 时序 IR 来自M 1.微命令发生器 电位型 脉冲型 功能: 产生全机所需的各种微命令 控制最基本的操作(微操作)的命令

送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU PC 地址形成 运行状态 微命令 发生器 D θ 寻 PSW 时序 IR 来自M 2.指令计数器PC 功能: 指示指令在M中的位置。 PC+1 顺序执行: PC先+1,再用转移地址修改PC 转移执行:

送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU 地址形成 运行状态 D θ 寻 PSW 时序 IR 来自M PC 微命令 发生器 IR 3.指令寄存器IR 功能: 存放现行指令。 决定操作性质 操作码字段 译码器 微命令发生器 寻 操作数地址 转移地址 地址码字段 地址形成部件 D

送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU 地址形成 运行状态 D θ 寻 PSW 时序 IR IR 来自M PC 微命令 发生器 工作方式优先级TN Z V C PSW 4.状态寄存器PSW 功能: 指示程序运行方式,反映程序运行结果。 例. 某机的PSW 15 12 11 8 7 6 5 4 3 2 1 0

15 12 11 8 7 6 5 4 3 2 1 0 工作方式优先级 T N Z V C (1)条件码 C=1 进位 V=1 溢出 Z=1 结果为0 N=1 结果为负 反映程序运行结果 (2)跟踪标志 为程序查错设置的断点标志T。 T=1, 执行跟踪程序 程序 初始化置T为1 ... 跟踪程序 测试T ….. ...

15 12 11 8 7 6 5 4 3 2 1 0 工作方式 优先级 T N Z V C (3)优先级 为现行程序赋予优先级别,以决定是否响应外部中断请求。 程序优先级高于外部优先级,不响应 程序优先级低于外部优先级,可响应 (4)工作方式 PSW在CPU中,反映程序运行状态;控制/状态字在接口中,反映CPU命令、设备状态。 规定程序的特权级。 用户方式:禁止程序执行某些指令 核心方式:允许程序执行所有指令

送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU 地址形成 运行状态 D θ 寻 PSW PSW 时序 IR IR 来自M PC 微命令 发生器 分频器 振荡器 时序 产生脉冲型微命令,控制定时操作 5.时序线路 功能: 控制操作时间和操作时刻。 工作脉冲 产生电位型微命令,控制操作时间段 时钟脉冲 时钟周期(节拍)

送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU 地址形成 运行状态 D θ 寻 PSW PSW 时序 IR IR 来自M PC 微命令 发生器 时序 3.3.2 控制器工作过程 1.取指令 地址 指令 PC M IR 、译码(θ、寻址方式) PC+1 PC

送M 微命令序列 PC +1 I/O状态 控制台信息 微命令 发生器 …... 译码 送M或ALU 地址形成 运行状态 D θ 寻 PSW PSW 时序 IR IR 来自M PC 微命令 发生器 时序 2.取数 按寻址方式,或从寄存器取数,或从存储器取数。 3.执行 按操作码对数据进行运算处理。

3.3.3 时序控制方式 即时序信号与操作的关系 1.组合逻辑控制器的时序划分 工作脉冲1 ●采用三级时序系统: 工作脉冲2 时钟周期1 ….. (节拍1) 工作脉冲k 工作周期1 时钟周期2 (节拍2) 工作周期2 ………. …. 指令周期 …… 时钟周期m (节拍m) 工作周期n ….

● 时序关系: 晶振输出 工作脉冲P 对微操作定时 打入IR 打入PC 时钟T1 控制分步操作时间 取出指令 时钟T2 修改PC 工作周期1 控制不同阶段操作时间 取指 工作周期2 取数 工作周期3 执行 指令周期

2.时序控制方式及其变化 由CPU或其他设备提供 (1)同步控制 ①定义: 各项操作受统一时序控制。 各项操作受统一时序控制。 ②特点: 各步操作的衔接、各部件之间的数 据传送受严格同步定时控制。 时钟周期时 间固定, 有明显时序时间划分, ③优缺点: 时序关系简单,时序划分规整, 控制不复杂; 控制逻辑易于集中,便于管理。 时间安排不合理。 ④应用场合: 用于CPU内部、设备内部、系 统总线操作 (各挂接部件速度相近,传送时间确 定,传送距离较近)。

(2)异步控制 总线 ①定义: 各项操作按不同需要安排时间,不 受统一时序控制。 ②特点: 无统一时钟周期划分, 各操作间的 衔接和各部件之间的信息交换采用异步应答 方式。 例.异步传送操作 ●主设备: 主 从 申请并掌握总线权的设备。 ●从设备: 发/接 接/发 响应主设备请求的设备。

●操作流程: 主设备输出端与总线连接 从设备准备好? 主设备获得总线控制权 主设备询问从设备 N Y 主设备发送/接收数据 主设备释放总线控制权 主设备输出端与总线断开

③优缺点: 时间安排紧凑、合理; 控制复杂。 ④应用场合: 用于异步总线操作(各挂接部 件速度差异大,传送时间不确定,传送距离 较远)。 (3)同步方式的变化 ①不同指令安排不同时钟周期数 指令周期长度可变,时钟周期长度不变。 ②总线周期中插入延长周期 经总线传送一次数据所用的时间(送地址、读/写)

T1 T1 T2 T2 T3 T3 T4 T4 时钟 时钟 T4 T4 Tw 总线周期长度可变,时钟周期长度不变。 例.一个总线周期包含4个时钟周期 送地址 读/写数据 结束 同步方式 总线周期(4T) 结束 送地址 读/写数据 总线周期(5T) 扩展同步方式

③同步方式引入异步应答 RQ/GT 以固定时钟周期作为时序基础,引入应答思 想。 例.8088最大模式,用一根总线请求/应答线实现总线权的转移。 CPU使用总线 CPU使用总线 设备使用总线 CPU使用总线 若干时钟 若干时钟 设备请求总线权 设备释放总线权 CPU响应, 总线权交设备 CPU 设备 CPU 设备 CPU 设备

3.3.4 组合逻辑控制方式的优缺点及应用 1.组合逻辑控制方式 综合化简产生微命令的条件,形成逻辑式, 用组合逻辑电路实现; 执行指令时,由组合逻辑电路(微命令发生 器)在相应时间发出所需微命令,控制有关 操作。

2.优缺点 ● 产生微命令的速度较快。 ● 设计不规整,设计效率较低; ● 不易修改、扩展指令系统功能。 3.应用场合 用于高速计算机,或小规模计算机。

第四节 微程序控制器原理 3.4.1 微程序控制的基本思想 1. 若干微命令编制成一条微指令,控制实现 一步操作; 1. 若干微命令编制成一条微指令,控制实现 一步操作; 2. 若干微指令组成一段微程序,解释执行一 条机器指令; 2. 若干微指令组成一段微程序,解释执行一 条机器指令; 3. 微程序事先存放在控制存储器中,执行机 器指令时再取出。

3.4.2 组成原理 微命令序列 译码器 IR 微命令字段 微地址字段 微地址 形成电路 µIR PSW PC 微地址寄存器 控制存储器 CM µAR 1.主要部件 (1)控制存储器CM 功能: 存放微程序。 CM属于CPU,不属于主存储器。

微命令序列 译码器 IR 微命令字段 微地址字段 微地址 形成电路 µIR PSW PC 微地址寄存器 控制存储器 CM µAR (2)微指令寄存器 µIR 功能: 存放现行微指令。 微命令字段: 提供一步操作所需的微命令。 (微操作控制字段) 指明后续微地址的形成方式。 微地址字段: 提供微地址的给定部分。 (顺序控制字段)

微命令序列 译码器 IR 微命令字段 微地址字段 微地址 形成电路 µIR PSW PC 微地址寄存器 控制存储器 CM µAR (3)微地址形成电路 功能: 提供两类微地址。 微程序入口地址: 由机器指令操作码形成。 后续微地址: 由微地址字段、现行微地 址、运行状态等形成。

微命令序列 微命令序列 微命令序列 译码器 译码器 译码器 IR PSW 微命令字段 微地址字段 微命令字段 微地址字段 微命令字段 微地址字段 微地址 形成电路 µIR 取指微指令 取指微指令 PC 控制存储器 控制存储器 控制存储器 CM 微地址寄存器 µAR 2.工作过程 (1)取机器指令 微命令字段 微命令 取指微指令 译码器 主存 CM µIR 机器指令 IR

微命令序列 微命令序列 微命令序列 译码器 译码器 译码器 IR IR IR PSW 微命令字段 微地址字段 微命令字段 微地址字段 微命令字段 微地址字段 微命令字段 微地址字段 微命令字段 微地址字段 微地址 形成电路 微地址 形成电路 µIR 取指微指令 取指微指令 PC 微地址寄存器 微地址寄存器 控制存储器 控制存储器 控制存储器 控制存储器 控制存储器 CM 微地址寄存器 µAR 微地址 形成电路 (2)转微程序入口 首条微指令 入口 操作码 微地址形成电路 µAR CM µIR IR (3)执行首条微指令 微命令字段 微命令 µIR 译码器 操作部件

微命令序列 译码器 PSW PSW IR 微命令字段 微地址字段 微命令字段 微地址字段 微命令字段 微地址字段 微地址 形成电路 微地址 形成电路 µIR PSW 微地址寄存器 微地址寄存器 微地址寄存器 微地址寄存器 PC 微地址寄存器 控制存储器 CM µAR 微地址 形成电路 (4)取后续微指令 微地址字段 现行微地址 运行状态 后续微地址 微地址形成电路 µAR 后续微指令 CM µIR

微命令序列 译码器 PSW PSW IR 微命令字段 微地址字段 微命令字段 微地址字段 微命令字段 微地址字段 微地址 形成电路 微地址 形成电路 µIR PSW 微地址寄存器 微地址寄存器 微地址寄存器 微地址寄存器 PC 微地址寄存器 控制存储器 CM µAR 微地址 形成电路 (5)执行后续微指令 同(3) (6)返回 (存放取指微指令的固定单元)。 微程序执行完,返回CM

3.4.3 微指令格式和编码方法 1.格式分类 (1)垂直型微指令 一条微指令定义并执行一种基本操作。 优点: 微指令短、简单、规整,便于编写微 程序。 缺点: 微程序长,执行速度慢;工作效率低。 (2)水平型微指令 一条微指令定义并执行几种并行的基本操作。 优点: 微程序短,执行速度快。 缺点: 微指令长,编写微程序较麻烦。

3 3 3 3 4 4 4 AI BI ZO AOP MOP KK ST (3)混合型微指令 在垂直型的基础上增加一些不太复杂的并行 操作。 微指令不长,便于编写;微程序不长,执行 速度加快。 例.长城203微指令 常数 运算器输入控制 运算器输出控制 操作类型控制 访M、I/O控制 辅助操作

1 1 1 C0 R W 0 进位初值为0 1 进位初值为1 0 不读 1 读 0 不写 1 写 C0= R= W= 2.编码方法 (1)直接控制法 微命令按位给出。 例. 某微指令 不需译码,产生微命令的速度快; 信息的表示效率低。 微指令中通常只有个别位采用直接控制法。

加法器 3 AI A B R、C D、E R、C D、F 001 R A 010 C A 011 D B 010 C A 011 D B 100 F B (2)分段直接编译法 微命令由字段编码直接给出。 例.对加法器输入端进行控制。 微指令中设置AI字段,控制 加法器的输入选择。 C D 000 不发命令 微命令分组原则: 同类操作中互斥的 微命令放同一字段。 ? 不能同时出现 …

3 3 加法器 AI BI 000 不发命令 000 不发命令 A B R、C D、E R、C D、F 001 R A 001 R B 010 C A 010 C B 011 D A 011 D B 010 C A 011 D B 100 E A 100 F B 加法器A输入端的控制命令放 AI字段,B输入端的控制命令 放BI字段。 C D AI: BI: 操作唯一; 编码较简单; 一条微指令能同时 提供若干微命令,便于组织各种操作。

C A (3)分段间接编译法 微命令由本字段编码和其他字段解释共同给 出。 1) 设置解释位或解释字段 例. 1 A为某类命令 0 A为常数 C = 解释位 2) 分类编译 按功能类型将微指令分类,分别安排各类微 指令格式和字段编码,并设置区分标志。

寄存器传A 寄存器号 R A (4)其他编码方法 1) 微指令译码与机器指令译码复合控制 例. 机器指令 微指令 译码器 R1 译码器 001 A门

取指标志 变址标志 2) 微地址参与解释 微地址 微指令 例. 004 011 3.4.4 微地址形成方式 1.微程序入口地址的形成 功能转移 指令操作码 微程序入口 (1)一级功能转移 各操作码的位置、位数固定,一次转换成功。 入口地址=页号,操作码

CM 0F(8位) 10(8位) 无条件转 微地址2 无条件转 微地址1 例. 机器指令1 000F 0010 功能转移 入口地址=000FH 0页 机器指令2 微地址1 功能转移 微程序1 入口地址=0010H 微地址2 微程序2

(2)二级功能转移 各类指令操作码的位置、位数不固定, 需两 次转换。 指令类型标志 分类转: 区分指令类型 指令操作码 区分操作类型 功能转:

PLA (3)用可编程逻辑阵列PLA实现功能转移 入口地址 1 入口地址 2 IR 2.后续微地址的形成 (1)增量方式 以顺序执行为主,辅以各种常规转移方式。

CM 转移条件 C A+1 R 顺序:现行微地址+1。 跳步:现行微地址+2。 A 转移条件 C B B D A+1 无条件转移:现行微指令 给出转移微地址。 (条件不满足) A+2 条件转移:现行微指令给 出转移微地址和转移条件。 B C (条件满足) 转微子程序:现行微指令 给出微子程序入口。 D 微子程序 返回微主程序:现行微指 令给出寄存器号。 R

(2)断定方式 给定部分 断定条件 D(给定) A(条件) 由直接给定和测试断定相结合形成微地址。 微指令 给定后续微地址 高位部分 指明后续微地址低 位部分的形成方式 例. 微指令 16路分支 微地址10位, 约定: 位数可变 2位 01 微地址低4位为操作码,D给定高 位; 6 10 微地址低3位为机器指令源寻址方式 A= 7 编码,D给定高 位; 8路分支 11 微地址低3位为机器指令目的寻址方式 7 8路分支 编码,D给定高 位。

3.4.5 微程序时序安排 同步控制,用统一微指令周期控制各条微指 令执行。 时钟周期 二级时序: 微指令周期 P 微指令 打入 µIR 结果打 入目的 地, 读取后续 微指令 控制数 据通路 操作 后续微 地址打 入 µAR

3.4.6 微程序控制方式优缺点及应用 1.优点 (1)设计规整,设计效率高; (2)易于修改、扩展指令系统功能; (3)结构规整、简洁,可靠性高; (4)性价比高。 2.缺点 访存频繁 转移较多 未充分发挥数据 通路本身具有的 并行能力 (1)速度慢 (2)执行效率不高 特别适用于系列机 3.应用范围 用于速度要求不高、功能较复杂的机器中。

第五节 主机和外部设备的信息交换 I/O I/O I/O 3.5.1 主机和外设的连接方式 1.辐射式 主机 主机 I/O I/O I/O 接口 接口 早期:不易扩展 现在:便于扩展

2.总线式 总线 便于扩展 主机 接口 接口 I/O I/O 3.通道式 主机 并行能力 提高 通道 通道 I/O I/O I/O I/O

3.5.2 信息传送控制方式 空闲 工作 结束 1.直接程序传送方式 (程序查询) 用I/O指令编程实现信息传送。 (1)外设状态 00 01 启动 在接口中设 置状态字表 示这些状态。 再请求 空闲:调用前,设备不工作; 调用完 完成一次 工作 结束:调用后,设备完成工作。 10

(2)查询流程 外设工作完成? 启动外设 N Y 入/出操作 (3)优缺点 硬件开销小; 实时处理能力差,并行程度低。 (4)应用场合 对CPU效率要求不高的场合, 或诊断、 调试过程。

2.中断方式 (1)中断的引入 查询: 程序 程序 主机 等待 启动 交换数据 外设 空闲 工作 中断: 程序 程序 程序 主机 中断程序 请求 启动 交换数据 外设 空闲 工作 并行操作 (2)中断定义

CPU暂时中止现行程序的执行,转去执行为某个随机事态服务的中断处理程序。处理完毕后自动恢复原程序的执行。CPU暂时中止现行程序的执行,转去执行为某个随机事态服务的中断处理程序。处理完毕后自动恢复原程序的执行。 一条指令结束 时有中断请求? (3)中断流程 =1 允许响应中断 CPU内设置允许中断标志 (开中断) =0 不允许响应中断 (关中断) 开中断 启动外设 Y 响应 继续原程序 执行中断服务程序 返回 N 继续原程序