CPU Optimization

This overview explores the concept of Out-of-Order Execution (OoOE) in CPUs, showcasing how separate instruction and data caches optimize performance. It examines a practical example involving instruction and operand cache misses and analyzes execution times under sequential and reordered execution scenarios. The CDC 6600, renowned as the first computer to implement OoOE in 1964, is discussed. We delve into the role of reservation stations (buffers) and how they contribute to efficient CPU operation, demonstrating the critical impact of OoOE on modern computing performance.

CPU Optimization

E N D

Presentation Transcript

CPU Optimization Out-of-Order Execution (OoOE)

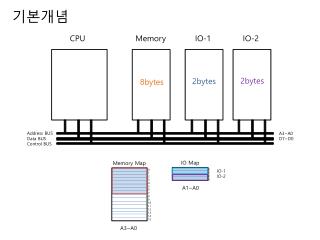

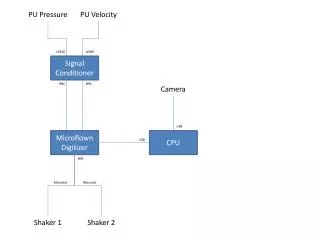

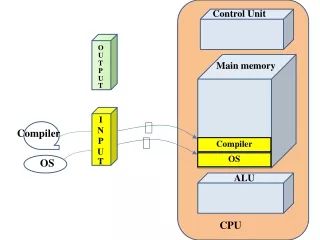

CPU with separate instruction and data caches FLASH RAM Instruction Cache Data Cache ALU

An Ideal Pipeline Pipeline with instruction & data cache Instruction NOT in cache Operand NOT in cache

Example: How long would this program take to execute? R1 = R2 R2 = R1 + R3 R4 = R3 + R5 *R3, R4, R5 Already in data cache

Sequential Execution Time = 12 Units Re-ordered Execution Time = 12 Units

The CDC 6600. The first computer to use OoOE (1964) Source: wikipedia