Interrupt

Learn about interrupts in the 8086 processor, how they break the program flow, and prioritize tasks. Understand interrupt handling for external devices and internal events to optimize program control.

Interrupt

E N D

Presentation Transcript

Interrupt • Interrupt – to break the flow of speech or action of (someone) by saying or doing something (Longman dictionary)

Examples • When your phone rings during a lecture, what will happen? • When you are studying then your cell phone rings – what will you do? • When you finish talking on the phone then you will continue with your study • Now your phone rings again and someone also knocking at your door then what will you do? • When being interrupted, you will perform some pre-defined action • Interrupt has priority – some interrupt is more important than the others. For example, answering your phone is more important than opening the door

Interrrupt is a procedure that interrupts whatever program is currently executing by the CPU. Interrupts are particularly useful when interfacing I/O devices that provide or require data at relatively low data-transfer rates , eg a keyboard. During an interrupt, the CPU will perform pre-defined operations according to the interrupt nature so the microprocessor can execute other software before the interrupt occurs Interrupts

Interrupt • Once the CPU is interrupted then it will perform the pre-defined operation according to the interrupt nature

Use of interrupt How to get key typed in the keyboard or a keypad? Polling The CPU executes a program that check for the available of data If a key is pressed then read the data, otherwise keep waiting or looping!!! Just like the mechanism used in LAB for sensing the keypad Interrupt The CPU executes other program, as soon as a key is pressed, the Keyboard generates an interrupt. The CPU will response to the interrupt – read the data. After that returns to the original program. So by proper use of interrupt, the CPU can serve many devices at the “same time” from the user’s point of view

Polling Vs Interrupt Polling interrupt Doing Something else No key pressed Return To original program Response To interrupt Do key pressed action

Example of interrupt • How to control a robot that has sensors to detect obstacles and makes a turn to avoid the obstacle • Polling • Move forward in a pre-defined unit • Check sensor reading • Do nothing if no obstacle or turn if obstacle detected • Loop back and move forward again

Interrupt • Controlling a robot by interrupt • Keeping moving until interrupted by the sensor • Interrupt received then do pre-defined operation • After finishing the interrupt service return to normal operation ie keep moving forward again

Polling Vs InterruptControl of a robot Move forward Move forward Check sensor Y interrupt Stop or turn

Interrupt Vs Polling • Which mechanism is better to controlling the robot if your objective is to move from point A to point B in the shortest time • Why??????

Introduction • Interrupt can be caused by an external device or an internal event • When interrupt occurs, program control is transferred from the original program to the Interrupt Service Routine (ISR) • The mechanism is similar to a subroutine call. The CPU remembers the location where it left off in the original program and then executes the interrupt service routine. After this routine has run to completion, program control is returned to the point where the CPU originally was executing.

Program flow with interrupt Original Program Interrupt service routine Interrupt occurs Return to the original program

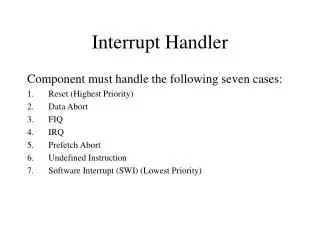

Introduction to interrupt • 8086 can implement 256 different types of interrupts • The interrupts are divided into 5 groups • Five groups: external hardware interrupt, software interrupts, internal interrupts, nonmaskable interrupt, and reset • The interrupt routines for external hardware, software, and nonmaskable interrupts can be defined by user (you can write your own ISR)

Introduction to interrupt • When more than one interrupt occur then priorities of the interrupts are compared in order to determine which interrupt to serve first (open the door or answer the phone?)

Interrupt Priority • Hardware, software, and internal interrupts are serviced on a priority basis • Priority hierarchy groups: internal interrupt, nonmaskable interrupt, software interrupt, and external hardware interrupt • Internal interrupt group has the highest priority • External hardware interrupt group has the lowest priority • Within a group, different interrupts have different priority levels represented by the type number (or interrupt number)

Interrupt priority • Type 0 – highest priority • Type 255 – lowest priority • Example – an internal interrupt, divide error, is a type 0 interrupt • Divide error : divide by zero • Overflow is type 4 • When a CPU is performing an interrupt service routine, it can be interrupted by a higher priority interrupt. If a lower priority occurs, the newly occurred interrupt must wait

Multiple interrupt Interrupt by Higher priority Interrupt

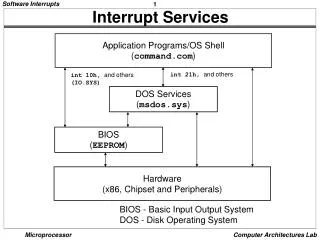

Interrupt address pointer table • When an interrupt occurs, CPU will perform some routine (function) • How to locate the appropriate function or where is the function stored in memory???? • In 8086, the interrupt address pointer table is serving as a link between the interrupt numbers to the locations of their service routines in memory

Function of interrupt pointer table Interrupt Address Pointer Table Interrupt Number Address (CS+IP) of Interrupt Service Routine

Interrupt Pointer Table • For 8086 the table is stored in memory location (address) 00H – 3FFH (1K) • Address pointers identify the starting locations (address) of their service routines in program memory. For the 8086, each pointer requires two words (4 bytes: segment + offset) • The higher address word is the base address and will be loaded into the CS register • The lower address word is the offset address and loaded into the IP register

Function of the pointer table Address of Service routine CS + IP Pointer table Interrupt Number/vector

Interrupt address table Vector 0 = interrupt type 0

Example • If INT50 occurs what are the addresses storing information for CS50 and IP50? This represent the interrupt level 50 Starting from 0 type 50 should be in 50x4 since each pointer requires 4 bytes In HEX, 200 is C8H to CBH (4 bytes) C8 stores the IP value, CA stores the CS

Interrupt pointer table FFFFFH Memory ISR for INT 200 AABBCH CS AABBH IP 000CH 00-3FFH Interrupt pointer table Interrupt No. 200

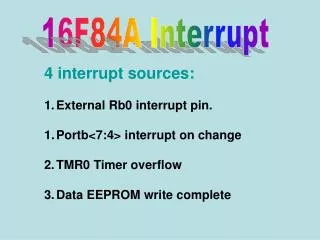

Interrupt in ADuC832 In ADuC832 The location for the ISR is fixed For example: The ISR for External Interrupt 0 (IE0) must be stored in memory location 0003H So the directive ORG is used to put the ISR to the proper address Example ORG 0003H ISR_IE0: … … IRET

Interrupt instruction • Int 80 – allows you to execute the Interrupt service routine for interrupt 80 in your program • Similar to a subroutine call but calling an ISR

Interrupt request input (INTR) • How can an external device interrupt the CPU? • The CPU has an input(s) pin for accepting the interrupt request signal • For 8086, this input pin is called INTR (interrupt request)

The Interrupt Flag • If the interrupt flag (IF)is set (=1) then external hardware can initiate an interrupt via the INTR input of the microprocessor • If IF flag is clear (=0) then the external device cannot initiate an interrupt • During the initiation sequence of an interrupt service routine, the 8086 automatically clears IF. This masks out (disable) the occurrence of any additional external hardware interrupt. • The IF flag should be re-enable at the end of the service routine

External hardware interrupt interface • An interrupt interface circuit is required to drive the INTR (Interrupt Request) input of the 8086 (WHY????) • There is only 1 interrupt input in the 8086 • The circuit will support external interrupt 32 to 255 • The circuit must identify which of the pending active interrupt has the highest priority and then pass its type number to the 8086 • The 8086 samples the INTR input during the last clock period of each instruction execution cycle

Interrupt interface circuit Interface circuit AD0-AD7 External Hardware interrupt 8086 CPU INTR INTA

External hardware interrupt • INTR =1 implies an active interrupt request • INTR is level-sensitive must be held at ‘1’ until it is recognized • INTR signal must be clear before the service routine runs to completion; otherwise, the same interrupt may be acknowledged again

Interrupt interface • INTA – interrupt acknowledge is used to inform the recognition of an interrupt • Two pulses are produced at INTA during the interrupt acknowledge bus cycle • The first pulse signals external circuit that the interrupt request has been acknowledged and to prepare to send the interrupt type number (or just the interrupt number) • The second pulse tells the external circuit to put the type number on the data bus • The type number is put on the bit 0 to 7 of the address/data bus

External Interrupt sequence • The interrupt sequence begins when an external device requests service by activating one of the interrupt inputs (32 to 255) • External circuit evaluates the priority of the input • If there is no interrupt already in progress and this interrupt is of higher priority than any other interrupt that is simultaneously active, the external circuit must issue a request for service to the 8086 • INTR switches to 1

Interrupt sequences • 8086 checks the setting of the IF • If IF is 0 then no interrupt action will be performed • If IF is 1 then external hardware interrupts are enabled and the service routine is to be initiated • Interrupt acknowledge cycle is initiated • T1 of the first bus cycle, address/data is put in the high-Z state and stays in this state for the rest of the cycle • During T2 and T3, /INTA (active-low) is switched to 0. And the INTR can be removed

Interrupt sequences • In the second interrupt acknowledge bus cycle, the INTA tells the external circuit to put the type number of the active interrupt on the data bus • External circuit put the type number on the data bus. This must be valid during T3 and T4 • DT/R, /DEN, and M/IO must set properly to read the type number from the data bus • After reading the type number, the interrupt acknowledge part of the interrupt sequence is completed

Interrupt acknowledge bus cycles Note: /INTA is issued twice

Interrupt sequences • After reading the type number, the corresponding interrupt service routine (ISR) is executed • Flag register is saved in the stack • IF is clear to disable other hardware interrupt • TF is clear to disable single-step mode if it is active • Current values of CS and IP are saved in the stack

Interrupt sequence • The type number is internally multiplied by 4, and the result is used as the address of the first word of the interrupt vector in the pointer table • Service routine is initiated • IRET at the end of the service routine causes the old contents CS and IP to be restored

Pay attention to the INTR

Before Acknowledge The IF flag must be 1 Ack Interrupt Type number is input at the 2nd INTA cycle Read Interrupt type Address of ISR is obtained by x4 the Interrupt type number and address the Interrupt pointer Table Call ISR IRET is reached Return to interrupted program

Interrupt service routine template To save registers and parameters on the stack PUSH XX PUSH YY PUSH ZZ Main body of the service routine To restore registers and parameters from the stack Return to main program POP ZZ POP YY POP XX IRET

Expanding interrupt input Can accept 7 inputs the /IRX input is used for supplying the Type No Priority is Resolve by storing The ISR at the Proper location A buffer/latch

Interrupt interface requirements • Support a many-to-one configuration • Able to issue the INTR signal • Able to supply the interrupt number to the CPU • Able to resolve priority issue

Interrupt interface using the NAND gate • The diagram in the previous page shows how to implement an interrupt interface using a simple NAND gate and a latch • The number of interrupt that can be supported is 7 !!!! (D7 is always a ‘1’) • The interrupt type number is derived from the active interrupt input • For example, if IR0 is active then the interrupt type number is 11111110 • For example, if IR1 is active then the interrupt type number is 11111101 • Using the previous circuit, can you handle two interrupts activated at the same time ?????

Resolving Priority issue • When two IRs (interrupt requests) active at the same time then we must serve the one with higher priority first • execute the ISR for higher priority interrupt • With the NAND gate and latch setup, we need to manipulate the interrupt pointer table

Resolving priority issue • If IR0 has a higher priority and if IR0 and IR1 active at the same time then the Interrupt type number received by the CPU is 11111100 (FCH) • CPU will go to location = FCH x 4 of the interrupt pointer table to look for the ISR • If we put the address of ISR for IR0 in that location then ISR of IR0 will be executed and implying that IR0 has a higher priority!

Interrupt pointer table Determine another address with the content CDABH Only IR0 active IR5 and IR0 active