PreProcessor Upgrade Issues

E N D

Presentation Transcript

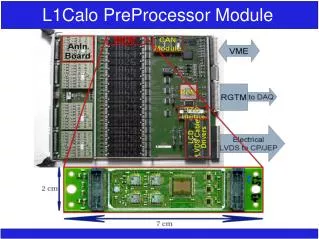

PreProcessor Upgrade Issues Victor Andrei Kirchhoff-InstitutfürPhysik (KIP) Ruprecht-Karls-Universität Heidelberg L1Calo Weekly Meeting, 10 January 2013

Current System to DAQ r/o data RGTM J 2 power LCD (f/o & routing) CP1 ch1 BCMUX LVDS-Tx ch2 FPGA 32x 10 C P ch3 CP2 to CP (LVDS cables) BCMUX LVDS-Tx ch4 480Mb/s FPGA 10 SUM LVDS-Tx FPGA (Spartan-6) to JEP (LVDS cables) MCM #1 FPGA J E P 16x JEP 480Mb/s FPGA MCM #16 PPM Virtex-II 2 L1Calo Weekly Meeting, 10/01/2013 V.Andrei, KIP

Phase-I: first solution to DAQ r/o data RGTM J 2 power nLCD (f/o & routing) CP1 ch1 BCMUX LVDS-Tx ch2 FPGA 32x 10 C P ch3 CP2 to CP (LVDS cables) BCMUX LVDS-Tx ch4 480Mb/s FPGA MUX + LVDS-Tx to JEP (LVDS cables) FPGA (Spartan-6) MCM #1 FPGA J E P 16x JEP 960Mb/s FPGA MCM #16 PPM Spartan-6/Artix-7 3 L1Calo Weekly Meeting, 10/01/2013 V.Andrei, KIP

Phase-I: second solution (A) Rear Extension to DAQ r/o data RGTM J 2 power to jFEX (optic fibers) nLCD (f/o & routing) CP1 ch1 SNAP12 BCMUX LVDS-Tx ch2 FPGA 32x 10 C P C P ch3 CP2 to CP (LVDS cables) BCMUX LVDS-Tx ch4 480Mb/s FPGA MUX + LVDS-Tx to JEP (LVDS cables) FPGA (Spartan-6) MCM #1 J E P FPGA J E P 16x JEP FPGA ? 960Mb/s FPGA MCM #16 PPM Spartan-6/Artix-7 Xilinx 7 Series 4 L1Calo Weekly Meeting, 10/01/2013 V.Andrei, KIP

Phase-I: second solution (B) Rear Extension to DAQ r/o data RGTM J 2 power to jFEX (optic fibers) LCD (f/o & routing) CP1 ch1 SNAP12 BCMUX LVDS-Tx ch2 FPGA 32x 10 C P C P ch3 CP2 to CP (LVDS cables) BCMUX LVDS-Tx FPGA ch4 480Mb/s FPGA 10 SUM LVDS-Tx to JEP (LVDS cables) FPGA (Spartan-6) MCM #1 J E P FPGA J E P 16x JEP 480Mb/s FPGA MCM #16 PPM Virtex-II Xilinx 7 Series 5 L1Calo Weekly Meeting, 10/01/2013 V.Andrei, KIP