Data Stream Managing Unit

Data Stream Managing Unit. Advisor : Vitaly Spector Students : Neomi Makleff Hadas Azulay Lab : High Speed Digital Systems. Introduction. There are interfaces with limited bandwidth (for example: PCI bus). HOWEVER, with ETHERNET we can increase the bandwidth. Project Aim.

Data Stream Managing Unit

E N D

Presentation Transcript

Data Stream Managing Unit Advisor : VitalySpector Students : NeomiMakleffHadasAzulay Lab : High Speed Digital Systems

Introduction • There are interfaces with limited bandwidth (for example: PCI bus). • HOWEVER, with ETHERNET we can increase the bandwidth.

Project Aim Creating a development environment in which we establish a line of communication between the managing software and the processing unit using LAN.

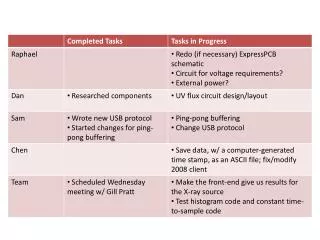

Development Environment - Hardware • PC • Altera PCI EXPRESS DEV KIT – STRATIX II GX (Rafael requirements) • Switch • Interface : Ethernet

Development Environment -Software • PC : Windows XP Professional • Altera PCI EXPRESS DEV KIT – STRATIX II GX: Nios II IDE Quartus II SOPC Builder

System Switch Ethernet PCIE NIOS II Processing unit

System Block Diagram PC JTAG JTAG Debug Module On chip Memory PHY Marvell GMII/MII Triple Speed Ethernet NiosII (*.ELF File) RJ-45 External Ethernet 10/100/1000 Mbps Flash Controller DDR2 Controller DDR2 SDRAM Flash memory

Output Example prep_tse_mac 0 Your Ethernet MAC address is 00:07:ed:ff:38:50 prepped 1 interface, initializing... [tse_mac_init] INFO : TSE MAC 0 found at address 0x14004000 INFO : PHY Marvell 88E1111 found at PHY address 0x12 of MAC Group[0] INFO : PHY[0.0] - Automatically mapped to tse_mac_device[0] INFO : PHY[0.0] - Restart Auto-Negotiation, checking PHY link... INFO : PHY[0.0] - Auto-Negotiation PASSED INFO : PHY[0.0] - Checking link... INFO : PHY[0.0] - Link established INFO : PHY[0.0] - Speed = 100, Duplex = Full OK, x=1, CMD_CONFIG=0x00000000 MAC post-initialization: CMD_CONFIG=0x04000203 [tse_sgdma_read_init] RX descriptor chain desc (1 depth) created mctest init called IP address of et1 : 192.168.1.234 Created "Inet main" task (Prio: 2) Created "clock tick" task (Prio: 3) Acquired IP address via DHCP client for interface: et1 IP address : 192.168.2.103 Subnet Mask: 255.255.255.0 Gateway : 192.168.2.1 Simple Socket Server starting up [sss_task] Simple Socket Server listening on port 30 Created "simple socket server" task (Prio: 4) [sss_handle_accept] accepted connection request from 192.168.2.100 [sss_handle_receive] processing RX data Value for LED_PIO_BASE set to 1. Value for LED_PIO_BASE set to 5. Value for LED_PIO_BASE set to 37. Value for LED_PIO_BASE set to 53.

Conclusions • Using the Simple Socket Server software template we checked if our system was functioning properly • The system succeeded to establish link at 100 Mbps • The system succeeded to connect to DHCP server and receive IP address • The PC succeeded to connect to the system using Port 30. • We were able to turn on/off LEDS by sending commands from the PC through the Ethernet