第十章 输入输出结构

770 likes | 935 Views

第十章 输入输出结构. 10.1 异步数据传输 10.2 可编程 I/O 10.3 中断 10.4 直接存储器访问 10.5 I/O 处理器 10.6 串行通信 10.7 实例:串行通信标准. 为了有效地执行功能,计算机除了能实现与存储器的交互,还应能与外部世界和设备交互信息,所有这些与计算机进行交互的设备可以归类为 输入输出设备( I/O 设备). 举例: 输入设备:键盘、鼠标、扫描仪 输出设备:显示器、打印机 输入 / 输出设备:硬盘、调制调解器. 第十章 输入输出结构. 10.1 异步数据传输 10.2 可编程 I/O 10.3 中断

第十章 输入输出结构

E N D

Presentation Transcript

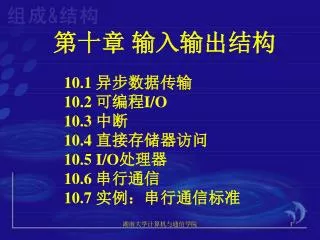

第十章 输入输出结构 10.1 异步数据传输 10.2 可编程I/O 10.3 中断 10.4 直接存储器访问 10.5 I/O处理器 10.6 串行通信 10.7 实例:串行通信标准 湖南大学计算机与通信学院

为了有效地执行功能,计算机除了能实现与存储器的交互,还应能与外部世界和设备交互信息,所有这些与计算机进行交互的设备可以归类为输入输出设备(I/O设备)为了有效地执行功能,计算机除了能实现与存储器的交互,还应能与外部世界和设备交互信息,所有这些与计算机进行交互的设备可以归类为输入输出设备(I/O设备) 举例: 输入设备:键盘、鼠标、扫描仪 输出设备:显示器、打印机 输入/输出设备:硬盘、调制调解器 湖南大学计算机与通信学院

第十章 输入输出结构 10.1 异步数据传输 10.2 可编程I/O 10.3 中断 10.4 直接存储器访问 10.5 I/O处理器 10.6 串行通信 10.7 实例:串行通信标准 湖南大学计算机与通信学院

输入/输出设备通过系统的地址总线、数据总线、控制总线和CPU相连(如图10.1)输入/输出设备通过系统的地址总线、数据总线、控制总线和CPU相连(如图10.1) 地址总线:单向 数据总线:单/双 控制总线:单向 图10.1 CPU与I/O设备的连接 湖南大学计算机与通信学院

根据是源还是目的设备启动传送以及是否使用 握手,异步数据传送可分为四种 • 不带握手的源启动数据传送 • 不带握手的目的启动数据传送 • 带握手的源启动数据传送 • 带握手的目的启动数据传送 湖南大学计算机与通信学院

10.1.1 源启动数据传送 源设备 输出数 据 选通控制信号并维持一段时间 目的设备读入数据 源设备使控 制信号和数 据无效 图10.2 不带握手的源启动数据传送 (a)时序 湖南大学计算机与通信学院

实现源数据传送更新LED的电路如图10.2(b) 图10.2 不带握手的源启动数据传送:(b)实现 每隔30秒,源设备向输出设备发送一个新值,输出设备将此值存贮于一个8位寄存器中; 寄存器的输出转换成相应的信号,在LED上显示两位数字。 湖南大学计算机与通信学院

10.1.1 目的启动的数据传送 目的设备读入数据后置数据选通信号无效 目的设备传输选通信号给源设备 一段时间后源设备使数据有效,并将数据稳定一段时间 源设备停止传输有效数据 图10.3 不带握手的目的启动数据传送 (a)时序 湖南大学计算机与通信学院

实现目的数据传送更新LED的电路如图10.3(b) 图10.3 不带握手的目的启动数据传送:(b)实现 当30秒时钟信号为高时,数据选通信号置1,选通三态缓冲器,使源设备传输有效数据,一个规定的延迟确保数据稳定后,目的寄存器读取数据,然后时钟信号为低,数据选通信号无效,有效数据不能传输。 湖南大学计算机与通信学院

10.3.1 握手 不带握手的数据传送无需确认数据收到,适合于在规定的时间内传送。 当每次传送所花费的时间不同时,设备可采用握手(handshaking)方式来协调数据传送。 湖南大学计算机与通信学院

带握手的源启动数据传送 源设备置数据请求信号为高,然后使有效数据可用 数据稳定后,目的设备读取此数据 目的设备读完数据,就发送一个数据确认信号给源设备 源设备停止传输有效数据,目的设备复位数据确认信号 图10.4 带握手的源启动数据传送 (a)时序 湖南大学计算机与通信学院

图10.4 带握手的源启动数据传送:(b)实现 当30秒时钟为高时,数据请求触发器置1; 数据请求信号也置1,并依次选通三态缓冲器,使有效数据对目的设备可用。 经一段延迟后,目的设备读取此数据并向源设备发送数据确认信号。 清除数据请求触发器,置数据请求信号为低并使数据无效。 最后数据确认信号置低。 湖南大学计算机与通信学院

带握手的目的启动数据传送 目的设备读完数据,就发送一个数据准备就绪信号给源设备 源设备停止传输有效数据,目的设备复位数据准备就绪信号 目的设备传输一个数据选通信号,源设备使有效数据可用 数据稳定后,目的设备读取此数据 图10.5 带握手的目的启动数据传送 (a)时序 湖南大学计算机与通信学院

图10.5 带握手的目的启动数据传送:(a)时序和(b)实现 湖南大学计算机与通信学院

第十章 输入输出结构 10.1 异步数据传输 10.2 可编程I/O 10.3 中断 10.4 直接存储器访问 10.5 I/O处理器 10.6 串行通信 10.7 实例:串行通信标准 湖南大学计算机与通信学院

可编程I/O(programmed I/O) 用指令编程来控制CPU输入或输出数据。 可编程I/O的编址方式 独立编址 有专门的指令访问I/O端口 存储器编址 把I/O端口视为存储器的一个单元,采 用存储器存取指令即可访问它们 湖南大学计算机与通信学院

相对简单CPU,其结构不能采用独立的I/O方式,但可利用存储器编址I/O方式 例:执行指令LDAC FFFF 为了实现此I/O端口,设计硬件如图10.6 当地址总线上的值为FFFFH,控制信号READ=1时,三态缓冲器才选通 图10.6 地址为FFFFH的输入端口 湖南大学计算机与通信学院

用相对简单的CPU设计自动调温器,它控制房间的加热和制冷系统,它可能执行下列操作:用相对简单的CPU设计自动调温器,它控制房间的加热和制冷系统,它可能执行下列操作: 由外部传感器读取温度; 如果(温度≥自动调温器的设置温度+2°),则打开空调; 如果(温度≤自动调温器的设置温度且空调打开),则关空调; 如果(温度≤自动调温器的设置温度-2°),则打开加热器; 如果(温度≥自动调温器的设置温度且加热器打开),则关加热器; 返回至1。 湖南大学计算机与通信学院

CPU从存储器编址输入端口地址FFFFH中读取当前温度CPU从存储器编址输入端口地址FFFFH中读取当前温度 CPU从端口地址FFFEH中获取调温器的设定温度 CPU向地址为FFFDH的输出端口中写入下面的值,以控制加热器和空调系统。 01=打开空调 02=关闭空调 03=打开加热器 04=关闭加热器 4. 当前状态存贮于存储单元1000H中 00=加热器和空调均关闭 FF=加热器打开 FE=空调打开 湖南大学计算机与通信学院

系统控制程序的算法如图10.7所示 湖南大学计算机与通信学院 图10.7 自动调温器控制算法

10.2.1 新指令 为了修改相对简单CPU以支持独立的I/O方式: 必须在CPU指令集中增加输入、输出指令; 产生必要的新控制信号; 在状态图中增加新状态; 开发RTL代码支持新状态; 修改寄存器、ALU和控制单元硬件来支持新的指令; 湖南大学计算机与通信学院

增加两条新指令:一条输入数据、一条输出数据。如表10.1所示 表10.1 相对简单CPU的独立I/O指令 湖南大学计算机与通信学院

增加一个新控制信号IO,IO=1时为I/O操作,IO=0时为存储器操作增加一个新控制信号IO,IO=1时为I/O操作,IO=0时为存储器操作 新状态 RTL代码 INPT1:DR←M,PC←PC+1,AR←AR+1 INPT2:TR←DR,DR←M,PC←PC+1 INPT3:AR←DR,TR INPT4:DR←输入端口 INPT5:AC←DR 湖南大学计算机与通信学院 图10.8 实现INPT指令执行周期的状态

硬件的修改 (1)修改寄存器; (2)修改ALU; (3)修改控制单元 湖南大学计算机与通信学院 图10.9 产生INPT执行周期的状态信号的硬件

计数器控制信号修改: INC=(INC原有值)∨ INPT1∨ INPT2∨ INPT3∨ INPT4 CLR=(CLR原有值)∨ INPT5 组合INPT1状态所需进行的修改: DRLOAD=(DRLOAD原有值)∨ INPT1 MEMBUS=(MEMBUS原有值)∨ INPT1 PCINC=(PCINC原有值)∨ INPT1 ARINC=(ARINC原有值)∨ INPT1 设定为IO=INPT4 存储器读=READ ∧ IOˊ 湖南大学计算机与通信学院

第十章 输入输出结构 10.1 异步数据传输 10.2 可编程I/O 10.3 中断 10.4 直接存储器访问 10.5 I/O处理器 10.6 串行通信 10.7 实例:串行通信标准 湖南大学计算机与通信学院

10.3.1 CPU和I/O设备之间的数据传送 解决I/O设备变化延迟 • 查询(polling) • 中断(interrupt) 减少由不确定性造成的延迟, 优化系统性能的一种机制 湖南大学计算机与通信学院

查询(polling) CPU I/O 传送数据 请求信号 准备好没有? 湖南大学计算机与通信学院

考察计算机系统的一个输入设备 CPU通过向I/O地址1001H中输出01H值,启动一个请求 然后不断查询输入端口1002H直至其最低位置1 继后CPU从输入端口1000H中读取数据 图10.10 采用查询方式实现I/O端口的硬件 湖南大学计算机与通信学院

查询方式在设计和编程方面都相对直观,常用于CPU负荷不很重的情况查询方式在设计和编程方面都相对直观,常用于CPU负荷不很重的情况 不适合对于CPU时间很宝贵的系统 等待状态(wait state) 处理器向I/O设备请求数据(或发送数据给I/O设备),I/O设备经控制总线向CPU发送一个等待信号。只要等待信号有效,CPU就一直处于等待状态 湖南大学计算机与通信学院

中断请求(interrupt request) 当I/O设备采用中断方式时,CPU在向I/O设备输出请求后,能够继续执行指令,完成有用的工作,而无需查询设备或进入等待状态 设备准备传输数据时,它向CPU发送中断请求信号 CPU响应中断,置中断响应信号有效,完成数据传输 湖南大学计算机与通信学院

10.3.2 中断类型 外部中断 CPU采用外部中断与输入/输出设备进行交互 内部中断 内部中断完全发生在CPU内部,没有任何输入/输出设备介入 软中断 由CPU指令集中的特定中断指令产生 湖南大学计算机与通信学院

10.3.3 中断处理 中断服务程序:处理中断工作的服务软件 一对一 或 一对多 一个中断服务程序对应一个中断 一个中断服务程序对应多个中断 湖南大学计算机与通信学院

不管是一个还是多个中断服务程序的配置方式,每个中断都执行下列事件 无操作(直至当前指令执行完 ) 获取中断服务程序地址(仅向量型中断) 调用中断服务程序 湖南大学计算机与通信学院

无操作(直至当前指令执行完 ) 考察相对简单CPU的LDAC指令的执行周期: LDAC1:DR←M,PC←PC+1,AR←AR+1 发生中断…… LDAC2:TR←DR,DR←M,PC←PC+1 LDAC3:AR←DR,TR LDAC4:DR←M LDAC5:AC←DR 如果执行周期完成后产生中断,则仅需保存PC的内容 否则必须保存CPU内部寄存器内容和控制单元的状态信息 湖南大学计算机与通信学院

获取中断服务程序地址(仅向量型中断) 向量中断 向CPU提供中断向量,此中断向量用于产生该中断的中断服务程序的地址 非向量中断 非向量中断在一个已知地址处读取中断服务程序 湖南大学计算机与通信学院

调用中断服务程序 阻止任何进一步的中断 2. 清除当前中断 ,避免一个中断请求 触发多于一个的中断 3. 确保返回主程序前所有相关的寄存 器保存原有值 湖南大学计算机与通信学院

10.3.4 中断硬件和优先级 非向量中断 (单个设备) 可用于简单 嵌入式控制器 湖南大学计算机与通信学院 图10.11 单个设备的非向量中断(a)硬件 (b)时序

向量中断 CPU必须从设备中读取中断向量,调用中断服务程序,程序的地址是该向量的一个函数 在这种结构中 如果在中断响 应前,设备取 消IRQ会发生 什么? 湖南大学计算机与通信学院 图10.12 单个设备的向量中断(a)硬件 (b)时序

非向量中断 (多个中断) 每个设备均有自己的IRQ和IACK信号 他们的优先级是预定的 ,IRQn优先级最高 CPU首先响应和服务优先级最高的中断 图10.13 多个非向量中断的硬件 湖南大学计算机与通信学院

向量中断 (菊花链方法) 菊花链:用于多中断优先权排队的一种方法 设备发出中断请求信号 CPU发出中断响应信号 图10.14 菊花链 设备n#接受IACK信号 IACK=0/传 给其他设备 IACK=1? N Y IACK=0 CPU读入中断向量/调用程序 湖南大学计算机与通信学院 一种可能的处理过程

IACKIN和IACKOUT所有的可能值、状态 表10.2 IACKIN和IACKOUT的可能值及其状态 湖南大学计算机与通信学院

并行优先权排队 菊花链将引起硬件延迟,特别是当链较长时,延迟就更大 通过一个优先权编码器采用并行优先权排队(parallel priority)方式实现向量中断,减少延迟 湖南大学计算机与通信学院

防止干 扰信号 图10.15 并行方式实现优先级中断 湖南大学计算机与通信学院

10.3.5 CPU内部实现中断 例:相对简单CPU 处理中断的过程 添加一个IRQ输入引脚,其响应信号传至IACK输出引脚 添加新指令LDSP、PUSHAC等 识别中断并访问此中断处理的状态 访问中断服务程序 湖南大学计算机与通信学院

表10.3 相对简单CPU的新指令 湖南大学计算机与通信学院

识别中断并访问此中断处理的状态 方法一 (a)采用分离的FETCH1状态和INT1状态 方法二 (IE′∨IP′)∧FETCH1 IE∧IP∧FETCH1 湖南大学计算机与通信学院 图10.16 两种访问中断服务程序的方法(b)修改FETCH1支持中断

访问中断服务程序(部分) INT1: AR←SP INT2: DR←PC[15..8],SP←SP-1 INT3: M←DR,AR←AR-1,SP←SP-1 INT4: DR←PC[7..0] INT5: M←DR INT6: DR←(数据总线来的向量) INT7: PC←1111,DR,0000,IP←0 湖南大学计算机与通信学院

第十章 输入输出结构 10.1 异步数据传输 10.2 可编程I/O 10.3 中断 10.4 直接存储器访问 10.5 I/O处理器 10.6 串行通信 10.7 实例:串行通信标准 湖南大学计算机与通信学院

直接存储器访问(DMA) 数据直接在I/O设备与存储器之间传送 DMA控制器 (通道) 实现直接存储器访问 湖南大学计算机与通信学院