Efficient Circuit Design with K-Maps: Minimization Techniques and Examples

Explore how to utilize "Don’t cares" in designing efficient circuits using K-maps. Learn about POS minimization, design techniques, and practical applications with illustrative examples. Enhance your knowledge on logic output optimization and circuit efficiency.

Efficient Circuit Design with K-Maps: Minimization Techniques and Examples

E N D

Presentation Transcript

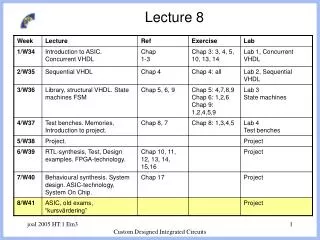

Lecture 8 Logistics Midterm 1 week from today Last lecture Verilog Last last lecture K-maps examples K-map high dimension example Don’t cares Today Don’t care (review) POS minimization with K-map Design examples with K-map

The “WHY” slide Don’t cares Sometimes the logic output doesn’t matter. When we don’t care if the output is 0 or 1, rather than assigning random outputs, it is best to denote it as “Don’t care.” If you learn how to use the “don’t care’s”, you will be able to build even more efficient circuits than without them. Design examples with K-map Doing K-map is fun, but when it is combined with an actual design problem you will see how k-map fits into the whole scheme of logic design.

Revisit Don’t cares example:Truth table for a BCD increment-by-1 INPUTS OUTPUTS A B C D W X Y Z0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 X X X X 1 0 1 1 X X X X 1 1 0 0 X X X X 1 1 0 1 X X X X 1 1 1 0 X X X X 1 1 1 1 X X X X • Function F computes the next number in a BCD sequence • If the input is 00102, the output is 00112 • BCD encodes decimal digits 0–9 as 00002–10012 • Don’t care about binary numbers 10102–11112

Example: with don’t cares F(A,B,C,D) = m(1,3,5,7,9) + d(6,12,13) F = A'D + B'C'Dwithout using don't cares F = A'D + C'Dusing don't cares A AB 00 01 11 10 CD Assign X == "1" allows a 2-cube rather than a 1-cube 0 0 X 0 1 1 X 1 1 1 0 0 0 X 0 0 00 01 D 11 C 10 B

POS minimization using k-maps Using k-maps for POS minimization Encircle the zeros in the map Interpret indices complementary to SOP form A AB 00 01 11 10 CD 1 0 0 1 0 1 0 0 1 1 1 1 1 1 1 1 00 01 D 11 C 10 B F = (B’+C+D)(B+C+D’)(A’+B’+C) Same idea as the Truth Table

Design example: a two-bit comparator A B C D LT EQ GT 0 0 0 0 0 1 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 0 0 1 0 0 0 0 1 0 1 0 1 0 1 0 1 0 0 1 1 1 0 0 1 0 0 0 0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 A B C D AB < CDAB = CDAB > CD LTEQGT block diagram truth table Need a 4 -variable Karnaugh map for each of the 3 output functions

Design example: a two-bit comparator (con’t) K-map for LT K-map for EQ K-map for GT A A A AB AB AB 00 01 11 10 00 01 11 00 01 11 10 10 CD CD CD 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 1 1 1 0 0 1 1 0 0 0 0 0 0 1 0 00 00 00 0 0 0 0 1 0 0 0 1 1 0 1 1 1 0 0 01 01 01 D D D 11 11 11 C C C 10 10 10 B B B LT = A'B'D+A'C+B'CD GT = BC'D'+AC'+ABD' EQ = A'B'C'D'+A'BC'D+ABCD+AB'CD' = (A xnor C)•(B xnor D)

Two ways to implement EQ: Design example: a two-bit comparator (con’t) A B C D EQ EQ Option 1: EQ = A'B'C'D'+A'BC'D+ABCD+AB'CD‘ 5 gates but they require lots of inputs Option 2 EQ = (A xnor C) •(B xnor D) XNOR is constructed from 3 simple gates 7 gates but they all have 2 inputs each

Design example: a two-bit comparator (con’t) Circuit schematics

Design example: BCD increment by 1 I8 I4 I2 I1 O8 O4 O2 O10 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 X X X X 1 0 1 1 X X X X 1 1 0 0 X X X X 1 1 0 1 X X X X 1 1 1 0 X X X X 1 1 1 1 X X X X O1O2O4 O8 I1I2I4 I8 block diagram truth table Need a 4 -variable Karnaugh map for each of the 4 output functions

Design example: BCD increment by 1 (con’t) I8 I8 I1 I1 I2 I2 I4 I4 I8 I8 I1 I1 I2 I2 I4 I4 O8 O4 0 1 X 0 0 1 X 0 1 0 X X 0 1 X X 0 0 X 1 0 0 X 0 0 1 X X 0 0 X X O8 = I4I2I1 + I8I1‘ O4 = I4I2' + I4I1' + I4'I2I1 O2 = I8'I2'I1 + I2I1‘ O1 = I1' O2 O1 1 1 X 1 0 0 X 0 0 0 X X 1 1 X X 0 0 X 0 1 1 X 0 0 0 X X 1 1 X X We greatly simplify the logic by using the don’t cares

Draw the circuit schematic O8 = I4I2I1 + I8I1' O4 = I4I2' + I4I1' + I4'I2I1 O2 = I8'I2'I1 + I2I1' O1 = I1' Design example: BCD increment by 1 (con’t)

Design example: a two-bit multiplier A2 A1 B2 B1 P8 P4 P2 P1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 1 0 1 1 0 0 1 1 1 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 0 0 0 0 0 0 1 0 0 1 1 1 0 0 1 1 0 1 1 1 0 0 1 P1P2P4 P8 A1A2 B1B2 block diagram truth table Need a 4 -variable Karnaugh map for each of the 4 output functions 9

A2 A2A1 A2 A2A1 00 01 11 10 00 01 11 10 B2B1 B2B1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 00 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 00 01 01 B1 B1 11 11 B2 B2 10 10 A1 A1 A2 A2 A2A1 A2A1 00 01 11 10 00 01 11 10 B2B1 B2B1 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 00 00 0 0 0 0 0 1 1 0 0 1 1 0 0 0 0 0 01 01 B1 B1 11 11 B2 B2 10 10 A1 A1 Two-bit multiplier (cont'd) P4=A2B2B1' +A2A1'B2 P8=A2A1B2B1 P1=A1B1 P2=A2'A1B2 +A1B2B1' +A2B2'B1 +A2A1'B1

Lecture 10 Logistics HW3 due Friday (cover materials up to this lecture) Lab3 going on this week Midterm 1: a week from today --- material up to this lecture Last lecture Don’t cares POS minimization with K-map K-maps design examples Today "Switching-network" logic blocks (multiplexers/demultiplexers)

Switching-network logic blocks Multiplexer (MUX) Routes one of many inputs to a single output Also called a selector Demultiplexer (DEMUX) Routes a single input to one of many outputs Also called a decoder multiplexer demultiplexer • We construct these • devices from: • logic gates • networks of tran- • sistor switches control control

The “WHY” slide Multiplexers/Demultiplexers If you had the ability to select which input to operate, the same part of a circuit can be used multiple times. So if you have a lot of inputs and all of them are supposed to go through same complex logic functions, you can save a lot of space on your circuit board by using a multiplexer. Then you will also need a demultiplexer to decode the output coming out in serial into separate output ports.

“WHY”: Sharing complex logic functions Share an adder: Select inputs; route sum A0 A1 B0 B1 Sb MUX MUX B A Sum Ss DEMUX Z0 Z1 multiple inputs Sa single adder multiple output destinations

Multiplexers Basic concept 2n data inputs; n control inputs ("selects"); 1 output Connects one of 2n inputs to the output “Selects” decide which input connects to output Two alternative truth-tables: Functional and Logical In1 In0 S Z0 0 0 00 0 1 00 1 0 10 1 1 01 0 0 01 0 1 11 1 0 11 1 1 1 S Z0 In01 In1 Functional truth table Logical truth table Example: A 2:1 Mux Z = SIn1 + S'Ino I0 Z S I1

Multiplexers (con't) 2:1 mux: Z = S'In0 + SIn1 4:1 mux: Z = S0'S1'In0 + S0'S1In1 + S0S1'In2 + S0S1In3 8:1 mux: Z = S0'S1'S2'In0 + S0'S1S2In1 + ... I0I1 I0I1I2I3 I0I1I2I3I4I5I6I7 2:1mux Z 4:1mux Z 8:1mux Z S0 S0 S1 S0 S1 S2

Logic-gate implementation of multiplexers 2:1 mux I0 S I1 4:1 mux I0 I1 I2 I3 Z Z Z S0 S1

Cascading multiplexers Can form large multiplexers from smaller ones Many implementation options 8:1 mux 8:1 mux I0I1I2I3 I0I1 2:1mux 4:1mux I2I3 2:1mux 2:1mux Z 4:1mux Z I4I5I6I7 4:1mux I4I5 2:1mux I6I7 2:1mux S0 S1 S2 S1 S2 S0

Multiplexers as general-purpose logic A 2n:1 mux can implement any function of n variables A lookup table A 2n – 1:1 mux also can implement any function of n variables Example: F(A,B,C) = m0 + m2 + m6 + m7 = A'B'C' + A'BC' + ABC' + ABC = A'B'(C') + A'B(C') + AB(0) + AB(1) A B C F0 0 0 10 0 1 00 1 0 10 1 1 01 0 0 01 0 1 01 1 0 11 1 1 1 10100011 01234567 C'C'01 C'C'01 0123 F F 8:1 MUX 4:1 MUX S1 S0 S2 S1 S0 A B A B C

Multiplexers as general-purpose logic Implementing a 2n-1:1 mux as a function of n variables (n-1) mux control variables S0 – Sn–1 One data variable Sn Four possible values for each data input: 0, 1, Sn, Sn' Example: F(A,B,C,D) implemented using an 8:1 mux A AB 00 01 11 10 1D01D'DD'D' CD 01234567 Choose A,B,C as control variables Choose D as a data variable 1 0 1 1 1 0 0 0 1 1 0 1 0 1 1 0 00 8:1 MUX F 01 D 11 C S2 S1 S0 10 B A B C

Demultiplexers (DEMUX) Basic concept Single data input; n control inputs (“selects”); 2n outputs Single input connects to one of 2n outputs “Selects” decide which output is connected to the input When used as a decoder, the input is called an “enable” (G) 1:2 Decoder: Out0 = G S' Out1 = G S 2:4 Decoder: Out0 = G S1' S0' Out1 = G S1' S0 Out2 = G S1 S0' Out3 = G S1 S0 3:8 Decoder: Out0 = G S2' S1' S0' Out1 = G S2' S1' S0 Out2 = G S2' S1 S0' Out3 = G S2' S1 S0 Out4 = G S2 S1' S0' Out5 = G S2 S1' S0 Out6 = G S2 S1 S0' Out7 = G S2 S1 S0

Logic-gate implementation of demultiplexers 1:2 demux G Out0 Out1 Out2 Out3 S1 S0 2:4 demux Out0 G S Out1

Demultiplexers as general-purpose logic A n:2n demux can implement any function of n variables DEMUX as logic building block Use variables as select inputs Tie enable input to logic 1 Sum the appropriate minterms (extra OR gate) demultiplexer “decodes” appropriate minterms from the control signals 0 A'B'C'1 A'B'C2 A'BC'3 A'BC4 AB'C'5 AB'C6 ABC'7 ABC 3:8 Demux 1 S2 S1 S0 A B C

Demultiplexers as general-purpose logic Example F1 = A'BC'D + A'B'CD + ABCD F2 = ABC'D' + ABC F3 = (A'+B'+C'+D') 0 A'B'C'D'1 A'B'C'D2 A'B'CD'3 A'B'CD4 A'BC'D'5 A'BC'D6 A'BCD'7 A'BCD8 AB'C'D'9 AB'C'D10 AB'CD'11 AB'CD12 ABC'D'13 ABC'D14 ABCD'15 ABCD F1 4:16Demux Enable = 1 F2 F3 A B C D

Cascading demultiplexers 5:32 demux 0 A'B'C'D'E'1234567 012 A'BC'DE'34567 3:8 Demux 3:8 Demux S2 S1 S0 S2 S1 S0 0123 2:4 Demux F S1 S0 01234567 ABCDE 0 AB'C'D'E'1234567 AB'CDE A B 3:8 Demux 3:8 Demux S2 S1 S0 S2 S1 S0 C D C D E E

Programmable logic (PLAs & PALs ) Concept: Large array of uncommitted AND/OR gates Actually NAND/NOR gates You program the array by making or breaking connections Programmable block for sum-of-products logic • • • inputs ANDarray ORarray productterms outputs • • •

All two-level logic functions are available You "program" the wire connections A 3-input, 5-term, 4-function PLA