EEPROM Workshop One EEPROM Page Anomaly Study

EEPROM Workshop One EEPROM Page Anomaly Study. G.Clifford D.Silver 321.676.7596 gclifford@silvereng.com. Overview. Hitachi 128k x 8 EEPROM’s Have Occurrences Of Page Write Failures

EEPROM Workshop One EEPROM Page Anomaly Study

E N D

Presentation Transcript

EEPROM WorkshopOne EEPROM Page Anomaly Study G.Clifford D.Silver 321.676.7596 gclifford@silvereng.com

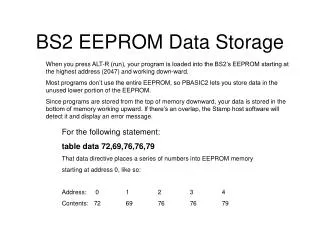

Overview • Hitachi 128k x 8 EEPROM’s Have Occurrences Of Page Write Failures • SEI Has Experienced 3 Such Failures In The Course Of Producing EDM & Flight Cards For The SECCHI & LAT Instrument Avionics • One Of The EEPROM Failures, SN0943 U50, Exhibits Consistent And Quick Time To Failures For The Same Single 128 Byte Page • This Presentation Provides Observations Particular To This One EEPROM Part Anomaly

Background • In July 04, One Of Several EDM Cards (SN0943) Produced For The GLAST LAT Instrument, Exhibited Data Failures Days After Writing Memory Locations • Memory Loss Was Located To A Single Page Of A Hitachi Die Within An MCM Packaged By Austin Industries, Part Number AS8ER128K32Q-150, Engineering Sample, U50 • Unlike Previously Observed Intermittent Page Failures, U50 Exhibits Repeatable Page Failures Shortly After Writing For The Same Page Location

Data Bit 16 Within Page Anomaly • Scope Set To Infinite Persistence As Address Sequenced Throughout Page With Anomaly

Read Access Excluding Page Anomaly • Scope Set To Infinite Persistence To Capture Any Unstable Cycles • No Other Page Anomalies Found

Anomaly Characteristics • The PCI Bridge FPGA Was Modified To Increase The Access Time For The EEPROM Read Cycle To 5uS • Following Slides Depict Anomaly Characteristics Of EEPROM Output Data Signals

Test Setup • Test Fixture Consisted Of An Open Frame cPCI Mother Board To Support Probe Access • VMEtro Provided cPCI Cycles

Anomaly Characteristics • D16 & D17 Fail Normal Access • All Failures Result In A Zero Being Read As A One

Anomaly Characteristics • Example Of Sustained Instability

Anomaly Characteristics • Example Of A Higher Frequency Sustained Instability

Anomaly Characteristics • Late Access Instability

Anomaly Characteristics • Zero Level Instability

Anomaly Characteristics • One Level Instability

Anomaly Characteristics • Late Level Determination

Bit Examinations • EEPROM Page Data Bits Were Measured And Recorded • The Following Charts Depict Definitions As Defined Below • All Cells With Background Color Of Yellow Should Have Had A Zero Value

Write One Location Test • One Location, EE ADDRESS 7400H, Was Written With An All Zero Data Byte • Writing One Location To The EEPROM Results In A Refresh Of Locations 7401H-7407H • Locations 7401H-7407H Recovered Many Of The Zero Bit Levels, All But 4 Bit Locations • Data Was Verified 1 Month & 4 Months Later • Bits That Recovered From A One To Zero Where Still Zero Levels And Location 7400H Was Still At 00H • Locations Failed Again Once Re-Written With A Full Page Write Cycle

Locations Not Re-Written • All Memory Locations Approached An FFH Data Value Over Time Except For The Following Locations • Two Locations In Page Maintained Proper Data Over Time, 741DH & 742CH • Locations 744FH & 745EH Were Degrading To FFH Data Values

Observed EEPROM Failures • SECCHI Instrument • FMA Observed Single Page Errors During TVAC, U25 (LDC 0208), After Device Was Re-Written Could Not Reproduce The Failure, Part Replaced On FMA • FMB Observed Single Page Errors U32 (LDC 0249), Scope Pictures Captured Of Oscillating Outputs, After Part Was Re-Written The Failure Could Not Be Reproduced • Part Was Removed And Tested By Austin Semiconductor With No Problems Found • Part Was Re-Installed On SECCHI EDM Card, Could Not Recreate The Problem

SECCHI U32 Page Failure • Page Failure Was Identified In JUN04 With A SECCHI EEPROM Flight Part • Austin Semiconductor AS58C1001SF-15/883C

Write Cycle Timing • Due To The Page Write Failures, Extensive Analysis Was Performed On Write Cycle Timing • SECCHI Design

Write Cycle Margins • Write Cycle Margins

RESET Signal Timing • Reset Circuit Characteristics • SECCHI FMA Power Up Power Down

Vcc Noise Measurements, Pin 61 • Vcc Noise Measurements During Read Access Anomaly

Vcc Noise Measurement Closeup • Vcc Noise Appears To Be Reacting To Output Signal Oscillations

VCC PIN 61 SCOPE GND VCC PIN 27 SCOPE GND Noise Measurement Points • Oscilloscope Noise Measurement Points

History Of Page Failures • JPL Mars Explorer Rover (MER) NVM_CAM Breadboard [1] • JPL MER RAD6000 (PFR#Z79906) [1] • Cassini Bail Board, Half Page Failure [1] • Deep Impact – HRI [1] • Mars 98 RAD6000 [3] • FHLP RAD6000 [3] • This above data primarily gathered by JPL to understand the MER & Genesis Failures • Aerospace AGE Testing, Two Incidences [2]

Summary • The Mechanism For Page Write Failures Does Exist Within The 128k x 8 Hitachi Dies • Stored Data Values Degrade Over Time To A Logical One Value • SN0943 U50 Represents An Example Of A Device With Consistent Single Page Failures • Other Devices Have Exhibited Intermittent Page Write Failures With Longer Time To Fail Characteristics

References • [1] EEPROM Bit Failure Investigation, Yuan Chen, Rich Kemski, Leif Scheick, Frank Stott, Duc Nguyen, Tien Nguyen, Richard Bennett, Ken Erickson, Jet Propulsion Laboratory, California Institute of Technology, 4800 Oak Grove Drive, Pasadena, CA 91109 • [2] Experiences in Qualifying a Commercial MNOS EEPROM for Space, E. E. King, R. C. Lacoe, G. Eng, and M. S. Leung, The Aerospace Corporation 2350 E. El Segundo Blvd. (310) 336-7898, everett.e.king@aero.org • [3] JPL Interoffice Memo, 514-DJS-03-073, Independent Team Review - EEPROM Bit Failures in the RAD6000