Distributed DLL

Distributed DLL. 學生:馮楷倫 指導教授:李泰成. Outline. Motivation System Architecture Circuit Details Behavior Simulation Results Conclusion. Introduction. Multiple-Phase Clock Generators Time-Interleaved System I/O Interface Circuits DLL-Based Frequency Multiplier Issues Phase Accuracy

Distributed DLL

E N D

Presentation Transcript

Distributed DLL 學生:馮楷倫 指導教授:李泰成

Outline • Motivation • System Architecture • Circuit Details • Behavior Simulation Results • Conclusion

Introduction • Multiple-Phase Clock Generators • Time-Interleaved System • I/O Interface Circuits • DLL-Based Frequency Multiplier • Issues • Phase Accuracy • Jitter Performance

Multiphase Clock Generation(i) • Time-interleaved System

Multiphase Clock Generation(ii) • Effect of timing error • Static timing error • Dynamic timing error

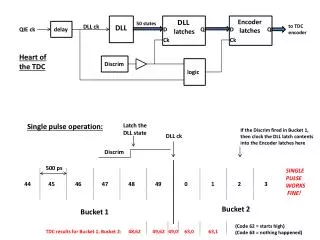

Conventional DLL Only one output phase is monitored.

Jitter Accumulation • Jitter accumulates along the delay line. • More delay cells = Larger jitter.

Distributed DLL(DDLL) • All output phases are monitored. • Reduce phase mismatch and jitter.

Locking Process of the DDLL Conceptual demonstration of the DDLL.

System Architecture Each delay cell is independently tuned.

PD Mismatch (i) PD mismatch will deteriorate the phase accuracy.

PD mismatch (ii) : the phase deviation caused by the ith PD : the phase deviation of the output of the ith delay cell

PD Rotation PD1 PD2 PD3 PD4 PD2 PD3 PD4 PD1 PD3 PD4 PD1 PD2 PD4 PD1 PD2 PD3

PD Mismatch (iii) The original With PD rotation

4 phases DDLL Architecture Delay Line Without PD rotation With PD rotation

V/I converter VI 1 (use VI sample1) & VI 3 (use VI sample2) VI 2 ( use both VI sample1&VI sample2)

V/I converter 1 Vdn represents the time difference between ck0 and ck1 Vup represents the time difference between ck1 and ck2 V/I 1 compares ⊿T01and ⊿T12

V/I converter 2 Vdn1 represents the time difference between ck0 and ck1 Vdn2 represents the time difference between ck1 and ck2 Vup1 represents the time difference between ck2 and ck3 Vup2 represents the time difference between ck3 and ck0 V/I 2 compares ⊿T02 and ⊿T20

V/I converter 3 Vdn represents the time difference between ck2 and ck3 Vup represents the time difference between ck3 and ck0 V/I 3 compares ⊿T23 and ⊿T30

Delay Cell Current-starved Delay cell Dcell

Behavior Model Simulation • ck0, ck1, ck2, ck3 come from the output clock of the behavior model • Give PD2 a 1ps time deviation intentional

Behavior Model Simulation (i) Without PD rotation (SNR = 67.3dB)

Behavior Model Simulation (ii) With PD rotation (SNR = 80.2dB)

Conclusion • By rotating the PDs, we can average out the timing error caused by the PD mismatch. • 1GHz reference clock, four clock phases output.

Future Word • Willing to tape out in this November. • Will use UMC65nm fabrication.