第六章 输入输出和中断技术

第六章 输入输出和中断技术. 本章内容 基本概念 I/O 端口的编址 输入输出的基本方法: 无条件 、 查询 、 中断 、 DMA 中断 中断基本概念 8086/8088 中断系统 8259 中断控制器 * DMA* DMA 的基本概念 DMA 工作过程 DMA 的三种传输方式 . 地址总线 AB. CPU. I/O 接 口. 输 出 设 备 O. I/O 接 口. 存 储 器 M. 输 入 设 备 I. 数据总线 DB. 控制总线 CB. 微型计算机中 I/O 接口的作用. CPU. I/O 接口

第六章 输入输出和中断技术

E N D

Presentation Transcript

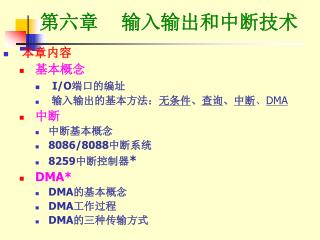

第六章 输入输出和中断技术 • 本章内容 • 基本概念 • I/O端口的编址 • 输入输出的基本方法:无条件、查询、中断、DMA • 中断 • 中断基本概念 • 8086/8088中断系统 • 8259中断控制器* • DMA* • DMA的基本概念 • DMA工作过程 • DMA的三种传输方式

地址总线 AB CPU I/O 接 口 输 出 设 备 O I/O 接 口 存 储 器 M 输 入 设 备 I 数据总线 DB 控制总线 CB 微型计算机中I/O接口的作用

CPU I/O接口 电路 I/O 设备 • 什么是I/O接口(电路)? • I/O接口是位于系统与外设间、用来协助完成数据传送和控制任务的逻辑电路,I/O接口就是CPU与外设的连接部件。 • PC机系统板的可编程接口芯片、I/O总线槽的电路板(适配器)都是I/O接口电路 接口在CPU与外设之间

6.1 输入/输出接口(I/O接口) • 6.1.1 概述 • I/O接口的定义 把外设连接到总线上的一组逻辑电路的总称。实现外设与主机之间的信息交换。 • I/O接口要解决的问题 • 速度匹配(Buffer) • 信号电平和驱动能力(电平转换器、驱动器) • 信号形式匹配(A/D、D/A) • 信息格式(字节流、块、数据包、帧) • 时序匹配(定时关系) • 总线隔离(三态门)

I/O接口的功能 • I/O地址译码与设备选择 • 把选中的与总线相接,未选中的与总线隔离(高阻态) • 数据的缓冲与暂存 • 缓解接口与CPU工作速度的差异 输出接口有锁存环节 输入接口有缓冲环节 • 对外设进行监测、控制与管理,中断处理 • 信号电平与类型的转换 • 形式、格式、电平、功率、码制等

6.1.2 I/O接口的编址方式 • I/O端口: I/O信息的三种类型:数据、命令、状态。 传送这三类信息的通道分别称为:数据端口(I、O)、命令端口(O)、状态端口(I)。 • 不同外设具有的端口数各不相同,计算机中为每一个端口都赋予一个惟一编号——称为端口地址(或端口号)。 • 端口有两种编址方式:统一编址和独立编址。

1. 统一编址 地址空间(共1MB) 0 • 定义 把外设接口与内存统一进行编址。各占据统一地址空间的不同部分。 • 优点 • 指令统一,灵活; • 访问控制信号统一,使用同一组的地址/控制信号。 • 缺点 • 内存可用地址空间减小 例如:MCS-51单片机 内存地址 (960KB) EFFFFH F0000H I/O地址 (64KB) FFFFFH

2. 独立编址 • 定义:外设地址空间和内存地址空间相互独立。 • 优点:内存地址空间不受I/O编址的影响 • 缺点:I/O指令功能较弱,使用不同的读写控制信号 例如:8088/8086 微机系统 内存地址空间 I/O地址空间 00000H 0000H I/O空间 (64KB) FFFFH 内存空间 (1MB) FFFFFH

20 16 8088/ 8086

MEMR、MEMW 8 0 8 8/8086 总 线 存储器访问 A19-A0 IOR、IOW 、AEN I/O访问 A15-A0 例如:8088/8086系统 D15/D7~D0 D15/D7~D0

8088/8086 CPU的I/O编址方式 • 采用I/O独立编址方式(但地址线与存储器共用) • 地址线上的地址信号用 来区分: • /0时为I/O地址/M地址 • I/O操作只使用20根地址线中的16/8根:A15/7~ A0 • 可寻址的I/O端口数为64K(65536)/256个 • I/O地址范围为0~FFFFH/0~FFH • IBM PC只使用了10根A9~ A01024个I/O地址(0~3FFH) 原因:够用为度, 简化电路

6.1.3 I/O端口地址的译码 I/O接口 (1端口) • 、 、 A15~ A0 OUT指令 将使总线的 信号有效 IN 指令 将使总线的 信号有效 当接口只有1个端口(仅数据口,无状态口和控制口)时,16位地址线一般应全部参与译码,译码输出直接选择该端口; 下面先介绍这种简单情况 当接口具有多个端口时,则16位地址线的高位参与译码(决定接口的基地址),而低位则用于确定要访问哪一个端口。 A0~A15 译码器 CS 例如: 某外设接口有4个端口(如8255/8253),地址为2F0H~2F3H,则其基地址为2F0H,由A15~A2译码得到,而A1、A0用来确定4个端口中的某一个。请思考:A0~A15=? I/O接口 (4端口) A0 A0 A1 A1 译码器 CS … A2~A15

6.1.4 I/O数据的传送方式 • 并行 • 定义:一个数据单位(通常为字节)的各位同时传送 • 特点:速度快、距离短、成本高 • 例如:PC机的并行接口(通常用于连接打印机) • 串行 • 定义:数据按位进行传送 • 特点:速度慢、距离远、成本低 • 例如:PC机的串行接口(通常用于串行通信)

6.2 简单接口电路 • 6.2.1 接口电路的基本结构 数据输入寄存器 (or 三态门) 译码 电路 数据线 AB (A0-A15) 数据输出寄存器 (锁存器) 接主机 接外设 DB (D0-D7) 状态线 状态寄存器 (or 三态门) 控制 逻辑 CB (IOR、IOW) 控制线 命令寄存器

接口电路的典型结构 AB 地址 译码 C P U 外 设 I/O端口1 (状态端口) DB 数据 缓冲 I/O端口2 (数据端口) 数据端口:用于存放CPU与外设间传送的数据信息 状态端口:用于暂存外设的状态信息 控制端口:用于存放CPU对外设或接口的控制信息, 控制外设或接口的工作方式。 CB 控制 电路 I/O端口3 (控制端口) 按存放信息的不同分类 • CPU对外设输入/输出的控制,通过对接口电路中各I/O端口的读/写操作完成。 • 端口 地址编号 • 从编程角度看,接口内部主要包括一个或多个CPU可以进行读/写操作的临时寄存器,又称I/O端口(Port)。 • 各I/O端口由端口地址区分(80X86 64K) ----编址方式 可用普通逻辑芯片(本章) 也可用专用接口芯片(下章)

接口电路的基本结构(续) • 数据输入/输出寄存器(缓冲器/锁存器) ——暂存输入/输出的数据。 • 命令寄存器(锁存器) ——存放控制命令,用来设定接口功能、工作参数和工作方式。 • 状态寄存器(缓冲器) ——保存外设当前状态,以供CPU读取。 • 一个外设一般占用端口地址情况 ——数据I/O、命令、状态三个寄存器各占一个端口地址(共3个);有时把命令、状态两个寄存器共占一个端口地址(共2个);一些简单外设只有数据寄存器一个端口(共1个)。 I/O接口可用普通门电路或专用电路制作

T2 T1 T3 T4 8088 CLK GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND VCC A15 A16/S3 A17/S4 A18/S5 A19/S6 SSO MN/MX RD HOLD HLDA WR IO/M DT/R DEN ALE INTA TEST READY RESET IO/M A19~A16 /S6~S3 A15~A8 AD7~AD0 A7 ~ A0 D7 ~ D0 ALE RD DT/R DEN 8088CPU最小模式下, I/O端口读周期时序

T2 T1 T3 T4 8088 GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND VCC A15 A16/S3 A17/S4 A18/S5 A19/S6 SSO MN/MX RD HOLD HLDA WR IO/M DT/R DEN ALE INTA TEST READY RESET CLK IO/M A19~A16 /S6~S3 A15~A8 AD7~AD0 A7 ~ A0 D7 ~ D0 ALE WR DT/R DEN 8088CPU最小模式下, I/O端口写周期时序

CPU总线I/O读、写时序(简化) T4 Tw T3 Tw T4 T2 T1 T3 T2 T1 CLK CLK A15~A0 A15~A0 D7~ D0 D7~D0 IOR IOW IN指令时序 OUT指令时序

简单接口电路(无条件传输) • 数据输入接口 • 必须具有三态输出能力,以便与总线挂接 • 外设有数据保持能力时—可用三态门实现 • 外设无数据保持能力时—用三态输出的锁存器实现 • 数据输出接口 • 常用锁存器实现

简单数据输入接口电路 • 三态门:高电平、低电平、高阻态 • 通常一个器件中包含8个三态门 • 常用芯片:74LS244(教材图6.3) • 应用例子:开关接口 • 工作波形图如下: A B E A0~A15 地址有效 IOR 译码输出 D0~D7 开关状态

简单的输入接口举例 编程实现如果所有开关都闭合,则程序转向标号NEXT1,否则转向NEXT2。 MOV DX,83FCH IN AL, DX AND AL,0FFH JZ NEXT1 JMP NEXT2 译码器 0 1 1 1 1 1 1 1 1 0 0 0 0 83FCH ~83FFH 0 0 0 0 0 输入设备 接口电路 系统总线

简单的输出接口举例 • 锁存器:由D触发器构成 • 通常一个器件包含:8个D触发器(+8个三态门) • 常用芯片:(教材图6.5、图6.6) • 74LS273(具有二态输出的D锁存器,内部结构见图6.5) • 74LS374(具有三态输出的D锁存器,内部结构见图6.8) • 应用例子:发光二极管接口 MOV DX,0FFFFH MOV AL,01000001B OUT DX,AL +5V 74LS273 R =1 D0 | D7 Q0 D0~D7 . . . . . . . . . . . . 功能: 第1、7个发亮,其余不亮 译 码 器 A0~A15 CP R =1 Q7 IOW 译码器具体连接见图6-6 输出设备 接口电路 系统总线 74LS374使用见图6-9

无条件传送方式(包括I/O) 数据 输出端口 选中地址 写信号 输入端口 读信号 无条件传送(I/O)

输入/输出接口综合应用例子 • 根据开关状态在7/8段数码管上显示数字或符号 • 共阳极7段数码管结构见p255 图6.10 • 用74LS273作为输出接口,把数据送到7段数码管 • 74LS273的地址假设为F0H • 用74LS244作为输入口,读入开关K0~K3的状态 • 74LS244的地址假设为F1H • 当开关的状态分别为0000~1111时,在7段数码管上对应显示’0’~’F’ • 7段码表见下面

共阳极、共阴极两种 a b f g e C d h a b c d e f g h a b c d e f g h com com 共阳极 共阴极

74LS273的端口地址:00F0 H = 0000 0000 1111 0000 B 74LS244的端口地址:00F1 H = 0000 0000 1111 0001 B D0 Q0 | Q1 D7 Q2 Q3 Q4 CP Q5 Q6 Q7 a b c d e f g h D0~D7 8个 反相器 译码电路 ≥1 IOW & 74LS138 A7~A4 G1 G2A G2B C B A Rx8 74LS273 7406 共阳极 7段数码管 ≥1 Y0 +5V A15~A8 K0~K3 D0 O1 I1 O2 I2 O3 I3 O4 I4 E1 A3 A2 D1 Y1 A1 D2 A0 D3 ≥1 IOR 开关 74LS244

相应程序段如下: …… Seg7 DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H DB 7FH,67H,77H,7CH,39H,5EH,79H,71H …… LEA BX, Seg7;取7段码表基地址 MOV AH, 0 GO:MOV DX, 0F1H ;开关接口的地址为F1H IN AL, DX ;读入开关状态 AND AL, 0FH ;保留低4位 MOV SI, AX ;作为7段码表的表内位移量 MOV AL, [BX+SI];取7段码 思考:可否改用XLAT? MOV DX, 0F0H ;7段数码管接口的地址为F0H OUT DX, AL JMP GO

CPU与外设间的数据传送方式 I/O接口电路基础:三态缓冲器/锁存器 问题:CPU与外设的工作速度不一致,尤其是当外设由其他CPU或时序电路控制时更加明显,应如何解决效率和可靠性。 数据传送控制:使两者高效、可靠地进行数据传送 四种传送方式 (1)无条件传送方式 (2)条件传送方式 ( 查询方式) (3)中断传送方式 (4)DMA传送方式 ( Direct Memory Access ) 存贮器直接存取方式 (程序方式)

IO总线 DB 三 态 缓冲器 开关 状态 D7 ~ D0 地址 译码 AB 284H A15 ~ A0 0 与 非 0 0 IOR 典型无条件传送方式接口电路(输入) 例: 开关 图中译码电路的作用: 只当A15~A0上出现284H时, (即0000 001010000100B) 输出0,其他输出1。 74LS244 E1/E2 该电路在CPU执行指令(当外设开关准备好后-开关动作时间固定) MOV DX, 284H IN AL, DX 功能:将输入设备的数据读入CPU内AL中

典型无条件传送方式接口电路(输出) IO总线 D7 ~ D0 数据线 锁存器 输出 设备 A15 ~ A0 地址 译码 地址线 288H 0 与 非 0 0 IOW 该电路在CPU执行指令(当外设LED指示灯准备好后—实际上一直处于准备好) MOV AL, 81H MOV DX, 288H OUT DX, AL 功能:CPU内AL中的数据81H送至输出设备 例:LED指示灯 74LS273 图中译码电路的作用: 只当A15~A0上出现288H时, (即0000 0010 1000 1000B) 输出0,其他输出1。

无条件传送方式(同步传送方式) (程序方式之一) • 实现方法 CPU不查询外设工作状态, 与外设速度的匹配通过在软件上延时完成, 在程序中直接用I/O指令,完成与外设的数据传送 • 特点 1. 适用于外设动作时间已知, 前提:CPU与外设进行数据传送时,外设保证已准备好。如开关、发光器件(如发光二极管、7段数码管、灯泡等)、继电器、步进电机等。 2. 软硬件十分简单。

从状态端口读入状态信息 N 外设准备好否? Y 从数据端口传送一个数据 (程序方式之二) 条件传送方式(查询传送方式) 编程流程 • 实现方法: 在与外设进行传送数据前,CPU先查询外设状态,当外设准备好后,再才执行I/O指令,实现数据传送。 • 特点: 1. CPU通过不断查询外设状态,实现与外设的速度匹配; 2. CPU的工作效率低,响应速度慢; 3. 适用于简单、慢速的或实时性要求不高的外设. 注意:多个外设时,查询流程见教材P259 图6.15-查询顺序代表了优先级

查询方式输入例 假设外设的状态端口为28C H(83H), 其中D7=1时,表示外设数据准备好 外设的数据端口为288 H(80H)。 实现从外设读50H个字节到内存缓冲区buffer中。 地址线 C P U 输入 外 备 地址 译码 28CH端口 状态端口 数据线 数据 缓冲 288H端口 数据端口 控制线 控制 电路 状态 信号 数据 信号 I/O接口

查询方式输入接口电路 PC总线 IOR 数据 端口 地址 译码 地址线 A15 ~ A0 288H 锁 存 器 三 态 缓冲器 数 据 线 D7 ~ D0 R Q D 三 态 缓冲器 D7 状态 端口 地址 译码 28CH D7 D6 D0 IOR BUSY & & READY GND MOV DX, 288H IN AL, DX 状态端口 D7=1 表示外设准备好 输 入 装 置 D0 : D7 READY STB +5v MOV DX, 28CH IN AL, DX

从28CH状态端口 读入外设状态信息 N Y Y D7=1, 外设准备好否? 从288H数据端口 读入一个字节数据 N 50H个数据传送结束? 流程图 编程从外设读入50H个字节到内存缓冲区buffer中

查询方式输入程序片段 思考:若状态口和数据口为83H和80H,则程序应如何修改? STATUS EQU 28CH MOV AX, SEG buffer ;取缓冲区首地址 MOV DS, AX LEA DI, buffer MOV CX, 50H ;传送个数 next:MOV DX, STATUS ask:IN AL, DX ;从状态端口读入状态信息 TEST AL, 10000000B ;80H, 检测D7位 JZask ;D7=0,继续查询 MOV DX, 288H IN AL, DX ;从数据端口读入数据 MOV [DI], AL ;送缓冲区 INC DI ;修改缓冲区指针 LOOP next ;传送下一个 ….

查询方式输出例 假设外设的状态端口为28C H, 其中D0 = 0时,表示外设准备好 外设的数据端口为288 H。 编程将缓冲区buffer的80H个字节输出到外设。 地址线 C P U 输出 外 备 地址 译码 28CH端口 状态端口 数据线 数据 缓冲 288H端口 数据端口 控制线 控制 电路 状态 信号 数据 信号 I/O接口

查询方式输出接口 IOW 数据 端口 地址 译码 地址线 A15 ~ A0 PC 总 线 288H 输 出 设 备 锁 存 器 D7 ~ D0 数 据 线 三 态 缓冲器 R D Q D0 状态 端口 地址 译码 +5v ACK D7 D6D0 28CH IOR & & BUSY MOV DX, 288H OUT DX, AL 状态端口 D0 = 0 表示外设准备好 READY (BUSY) MOV DX, 28CH IN AL, DX

从28CH状态端口 读入外设状态信息 N Y Y D0=0, 外设准备好否? 将一字节数据送至 288H数据端口 N 80H个数据传送结束? 条件查询输出流程图 编程将缓冲区buffer的80H个字节输出到外设

查询方式输出程序片断 STATUS_PORT EQU 28CH DATA_PORT EQU 288H MOV AX, SEG buffer ;取缓冲区首地址 MOV DS, AX LEA SI, buffer MOV CX, 80H ;传送个数 next:MOV DX, STATUS_PORT ask:IN AL, DX;从状态端口读入状态信息 TEST AL, 0000 0001B ;检测D0位 JNZ ask ;D0=1,继续查询 MOV AL, [SI] ;从缓冲区取数 MOV DX, DATA_PORT OUT DX, AL ;从数据端口输出数据 INC SI ;修改缓冲区指针 LOOP next ;输出下一个 ….

中断传送方式 • 实现方法: 1. 当外设准备好,向CPU发出中断请求 2. CPU在满足响应中断的条件下,发出中断响应信号; 3. CPU暂停当前的程序,转去执行中断服务程序, 完成与外设的数据传送; 4. CPU从中断服务程序返回,继续执行被中断的程序

外 设 发申请 中断服务程序 发申请 中断服务程序 中断方式下CPU执行程序流程 时间随机 两者无关 硬件中断---NMI 与INTR两根线申请中断(与CALL差别大) 软件中断---INT n与INTO指令(与CALL功能类似)

中断传送方式 4 1 3 2

中断过程大致分为: • 中断请求:由需要提供中断服务程序的设备提出; • 中断响应:CPU给设备发出一个中断应答信号; • 现场保护:保护执行中断服务程序前的各种信息; • 执行中断服务程序:完成特定的操作; • 退出中断服务程序:恢复现场。