Instruction Encoding

Instruction Encoding. MIPS machine language Binary encoding of instructions MIPS instruction = 32 bits Three instruction formats Different ways of specifying operands. Ch. 11 Instruction Encoding. Real MIPS Machine Instructions; Mapping pseudo instructions to real ones. R-type (register)

Instruction Encoding

E N D

Presentation Transcript

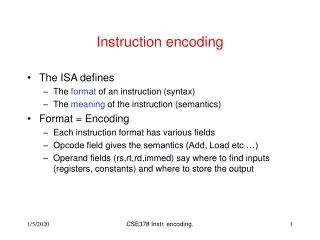

Instruction Encoding • MIPS machine language • Binary encoding of instructions • MIPS instruction = 32 bits • Three instruction formats • Different ways of specifying operands Comp Sci 251 -- instruction encoding

Ch. 11 Instruction Encoding Real MIPS Machine Instructions; Mapping pseudo instructions to real ones Comp Sci 251 -- instruction encoding

R-type (register) Arithmetic/logical (all register operands) Shift Jump register I-type (immediate) Arithmetic/logical (immediate operands) Load Store Conditional branch J-type (jump) Unconditional jump Jump and link MIPS instruction formats Comp Sci 251 -- instruction encoding

R-type instruction format 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits • Op + funct: instruction ID • rs, rt, rd: register operands • 5 bits: long enough for register ID number • rs, rt: source registers • rd: destination register • Shamt: shift amount (only used for shifts) • 5 bits: shift amount always in range 0..31 op rs rt rd shamt funct Comp Sci 251 -- instruction encoding

R-type examples add $5, $6, $7 sll $t6, $t7, 2 #($t6=$14 $t7=$15) 000000 00110 00111 00101 00000 100000 op (6) rs (5) rt (5) rd (5) shamt (5) funct (6) 000000 00000 01111 01110 00010 000000 Comp Sci 251 -- instruction encoding

R-type example jr $ra 000000 11111 00000 00000 00000 001000 op (6) rs (5) rt (5) rd (5) shamt (5) funct (6) Comp Sci 251 -- instruction encoding

I-type instruction format • Op: instruction ID • rs, rt: register operands • Immediate: branch target/immediate operand 6 bits 5 bits 5 bits 16 bits op rs rd immediate Comp Sci 251 -- instruction encoding

I-type example addi $1, $2, -3 001000 00010 00001 1111 1111 1111 1101 op (6) rs (5) rd (5) immediate (16) Comp Sci 251 -- instruction encoding

I-type examples lw $t0, 12($sp) sw $t0, -12($fp) 100011 11101 01000 0000 0000 0000 1100 op (6) rs (5) rt (5) immediate (16) 101011 11110 01000 1111 1111 1111 0100 Comp Sci 251 -- instruction encoding

I-type example beq $1, $2, top Immediate: distance to target 000100 00001 00010 ???? ???? ???? ???? op (6) rs (5) rt (5) immediate (16) Comp Sci 251 -- instruction encoding

PC-relative addressing • Used in branch instructions • Immediate field contains distance to target • Positive: branch forward • Negative: branch backward • Range: -32768…+32767 • Counts number of instructions, not bytes • Distance is measured from next instruction Comp Sci 251 -- instruction encoding

Example top: li $t0, 5 add $t0, $t0, $t1 beq $1, $2, top # distance = -3 sw $t0, x 000100 00001 00010 1111 1111 1111 1101 op (6) rs (5) rt (5) immediate (16) Comp Sci 251 -- instruction encoding

PC-relative addressing • Q: Why is distance measured from next instruction? • A: Fetch-Decode-Execute cycle • Fetch instruction & increment PC (add 4) • Decode instruction: get operands • Execute instruction: compute result, load or store Branch target = PC + 4 * distance Comp Sci 251 -- instruction encoding

J-type instruction format • Op: instruction ID • Target: (most of) jump address 6 bits 26 bits Op Target Comp Sci 251 -- instruction encoding

J-type examples j bottom # bottom = 0x00400058 0000 0000 0100 0000 0000 0000 0101 1000 jal f # f = 0x00400058 000010 0000 0100 0000 0000 0000 0101 10 Op (6) Target (26) 000011 0000 0100 0000 0000 0000 0101 10 Comp Sci 251 -- instruction encoding

Assembly language pseudo-instructions lw $t0, x # address=0x10010004 Machine language encoding? • Address of x takes up 32 bits – how do we keep it in lw instruction? • I-type instruction • Immediate field only 16 bits. How do we represent 32 bit immediate field • Problem? Comp Sci 251 -- instruction encoding

New instruction • Load upper immediate: lui rt, immediate • Immediate operand high-order 16 bits of rt • 0 low-order 16 bits • I-type instruction 001111 00000 rt immediate Comp Sci 251 -- instruction encoding

Use of lui and base register lw $t0, x # address=0x10010010 lui $at, 0x1001 lw $t0, 0x0010($at) • $at= "assembler temporary" • Used to implement pseudo-instructions Comp Sci 251 -- instruction encoding

Another lw problem – index addressing lw $t0, x($t1) # address of x # = 0x10010010 Problem? Requirement: x($t1)= address of x + contents of $t1. Problem: (32 bits) (32 bits) Solution: lui $at, 0x1001 add $at, $at, $t1 lw $t0, 0x0010($at) Comp Sci 251 -- instruction encoding

Load immediate pseudo-instruction li $t0, 0x12345678 • Problem? • Solution: lui $at, 0x1234 ori $t0, $at, 0x5678 Comp Sci 251 -- instruction encoding

Load immediate w/ small constant li $t0, 5 ori $t0, $0, 5 • Only one instruction needed • Constant fits into 16-bit immediate field • RISC design principle: "make the common case fast" Comp Sci 251 -- instruction encoding

Conditional branchpseudo-instructions • MIPS machine language: beq, bne (blez, bgtz, bltz, bgez) • All others are pseudo-instructions • New instructions: set-on-less-than slt rd, rs, rt if (rs < rt) rd = 1; else rd = 0; slti rt, rs, immed if(rs < immed) rt = 1; else rt = 0; Comp Sci 251 -- instruction encoding

Machine language blt implementation • MIPS machine language: beq, bne (blez, bgtz, bltz, bgez) • All others are pseudo-instructions Register operands blt $t0, $t1, foo # pseudo instruction # if($t0<$t1) goto foo slt $at, $t0, $t1 # if($t0<$t1) $at = 1 bne $at, $0, foo # if($at!=0) goto foo Comp Sci 251 -- instruction encoding

Machine language blt implementation Immediate operand blt $t0, 100, foo slti $at, $t0, 100 bne $at, $0, foo • Exercise: ble, bgt, bge Comp Sci 251 -- instruction encoding

Multiplication • 32-bit multiply 64-bit product • Where does the product go? • Special-purpose registers: Hi & Lo (each 32 bits) • Machine language multiply instruction mult $t0, $t1 # $t0 × $t1 Hi:Lo • Additional instructions: mfhi $t2 # Hi $t2 mflo $t3 # Lo $t3 Comp Sci 251 -- instruction encoding

mul pseudo-instruction # note immediate operand mul $t0, $t1, 123 ori $at, $0, 123 mult $t1, $at mflo $t0 Comp Sci 251 -- instruction encoding

Division • Hardware division operation produces both • quotient • remainder • Machine language divide instruction div $t0, $t1 # $t0 / $t1 Lo # $t0 % $t1 Hi Comp Sci 251 -- instruction encoding

div pseudo-instruction # note immediate operand div $t0, $t1, 123 ori $at, $0, 123 div $t1, $at mflo $t0 Comp Sci 251 -- instruction encoding