Data Redundancy Techniques for Error Detection and Correction

Learn about various information redundancy methods such as Parity, 1-Bit-per-Word, 2-Bit-per-Byte, 3-Bit-per-Chip, 4-Bit-per-Multiple-Chips, and Two-Dimensional Parity for detecting and correcting errors in data storage. These techniques offer varying levels of protection against data corruption in computer systems.

Data Redundancy Techniques for Error Detection and Correction

E N D

Presentation Transcript

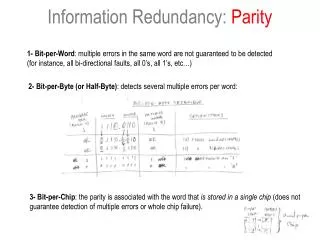

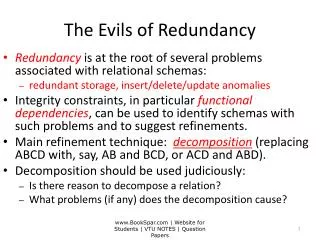

Information Redundancy: Parity 1-Bit-per-Word: multiple errors in the same word are not guaranteed to be detected (for instance, all bi-directional faults, all 0’s, all 1’s, etc…) 2-Bit-per-Byte (or Half-Byte): detects several multiple errors per word: 3-Bit-per-Chip: the parity is associated with the word that is stored in a single chip (does not guarantee detection of multiple errors or whole chip failure).

Information Redundancy: Parity 4-Bit-per-Multiple-Chips: detects the failure of a complete chip, BUT does not locate the chip. If a chip fails, only one bit per parity group is changed in all parity groups. 5-Two-Dimensional Parity: detects and corrects several errors on the matrix. vargas@computer.org