第 4 章 16 位微处理器

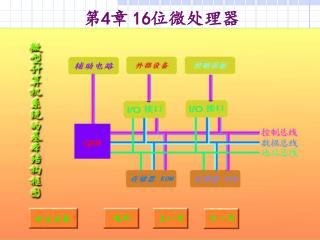

第 4 章 16 位微处理器. 时序 和 控制 逻辑. 指 令 译 码. 指 令 寄 存. 控制总线. 地址总线 控制. 通 用 寄存器组. 地 址 寄存器组. 地址总线. 数据总线 控制. 内部数据总线. 数据总线. 暂存器. 累加器. 标志寄存器. ALU. 第 4 章 16 位微处理器. 4.1 16 位微处理器概述 微处理器 (microprocessor) 是微型计算机的运算及控制部件,也称为中央处理单元 (CPU) 。通常微处理器由算术逻辑部件 (ALU) 、控制部件、寄存器组和片内总线等组成。见下图。.

第 4 章 16 位微处理器

E N D

Presentation Transcript

时序 和 控制 逻辑 指 令 译 码 指 令 寄 存 控制总线 地址总线 控制 通 用 寄存器组 地 址 寄存器组 地址总线 数据总线 控制 内部数据总线 数据总线 暂存器 累加器 标志寄存器 ALU 第4章16位微处理器 4.1 16位微处理器概述 • 微处理器(microprocessor)是微型计算机的运算及控制部件,也称为中央处理单元(CPU)。通常微处理器由算术逻辑部件(ALU)、控制部件、寄存器组和片内总线等组成。见下图。

第4章16位微处理器 4.1 16位微处理器概述 • 1971年,Intel公司设计了世界上第一个微处理器芯片Intel4004,开创了一个全新的计算机时代。 • 微处理器经历了许多代,集成度越来越高,功能越来越强,性能越来越高。 • 第1代:4位和低档8位微机 4004→4040→8008 • 第2代:中高档8位微机 Z80、I8085、M6800,Apple-II微机 • 第3代:16位微机 8086→8088→80286,IBM PC系列机 • 第4代:32位微机 • 80386→80486→Pentium→Pentium II →Pentium III →Pentium 4 • 32位PC机、Macintosh机、PS/2机 • 第5代:64位微机 Itanium、64位RISC微处理器芯片 微机服务器、工程工作站、图形工作站

第4章16位微处理器 Intel4004和采用4004的计算器

IBM PC系列机 8088CPU IBM PC机 IBM PC/XT机 IBM PC/AT机

英特尔微处理器芯片 Pentium 4 80386 Pentium

第4章16位微处理器 4.1 16位微处理器概述 • 本章介绍16位微处理器8086/8088的内部结构和工作原理。 • 8086和8088 CPU的内部基本相同,但它们的外部性能是有区别的。8086是16位数据总线,而8088是8位数据总线,在处理一个16位数据字时,8088需要两步操作,而8086只需要一步。 • 8086和8088 CPU的内部都采用16位字进行操作及存储器寻址,两者的软件完全兼容,程序的执行也完全相同。然而,由于8088要比8086有较多的外部存储操作,所以,对于相同的程序,它将执行得较慢。这两种微处理器都采用相同的40脚双列直插式(DIP)封装。 4.2 8086/8088 CPU的结构 • 8086/8088 CPU从功能上可分为两部分,即总线接口部件BIU(bus interface unit,缩写为BIU)和执行部件EU(execution unit,缩写为EU). 8086/8088 CPU的内部结构如下图所示:

8088的内部结构 地址加法器 20位 ∑ AH AL BH BL CH CL 8位 CS 通用 寄存器 DH DL DS SP SS 输入/输出控制电路 BP ES SI IP 外部总线 DI 内部暂存器 16位 执行部分控制电路 1 2 3 4 ALU 8位 指令队列 标志寄存器 总线接口部件 (BIU) 执行部件 (EU)

第4章16位微处理器 4.2.1 执行部件 • 执行部件EU的功能就是负责指令的执行,对指令进行译码,并利用内部的寄存器和ALU对数据进行所需的处理。 • 执行部件EU有下列部分组成: • 4个通用寄存器,即AX BX CX DX; • 4个专用寄存器,即基数指针寄存器BP、堆栈指针寄存器SP、源变址寄存器SI、目的变址寄存器DI; • 标志寄存器; • 算术逻辑单元。 • 说明: • 4个通用寄存器既可以作为16位寄存器使用,也可以作为8位寄存器使用。 • AX寄存器也称为累加器。许多指令都是利用累加器来执行的。 • 算术逻辑部件主要是加法器,绝大部分指令的执行都是由加法器完成的。 • 标志寄存器共有16位,其中7位未用,格式如下表所示,各位的含义见课本75页表4-1

第4章16位微处理器 • 根据功能,8086/8088的标志可以分为两类:一类叫状态标志,另一类叫控制标志。状态标志表示前面的操作执行后,ALU处于何种状态,该状态会影响后面的操作;控制标志是人为设置的,指令系统中有专门的指令用于控制标志的设置和清除,每个控制标志都对某一特定的功能起控制作用。 • 状态标志有6个,即SF、ZF、PF、CF、AF、OF。 • SF:符号标志,和运算结果的最高位相同,表示运算结果是正还是负。 • ZF:零标志,表示当前的运算结果是否为零,是则为1,否则为0。 • PF:奇/偶标志,如运算结果低8位中所含的1的个数为偶数,则为1,否则0 • CF:进位标志,当执行一个加法运算使最高位产生进位时,或者执行一个减法运算引起最高位产生借位时,CF为1,此外,循环指令也会影响这一标志。 • AF:辅助进位标志,如果当进行加法运算时,第三位向第四位进位,或者进行减法运算时,第三位从第四位借位,则AF为1。辅助进位标志一般在BCD码运算中作为是否进行十进制调整的判断依据。 • OF:溢出标志,运算结果产生溢出则为1,否则为0。 • 例题: 0010 0011 0100 0101 0101 0100 0011 1001 + 0011 0010 0001 1001 + 0100 0101 0110 1010 0101 0101 0101 1110 1001 1001 1010 0011 SF=0,ZF=0,PF=0,CF=0,AF=0,OF=0 SF=1,ZF=0,PF=1,CF=0,AF=1,OF=1

第4章16位微处理器 • 控制标志有3个,即DF、IF、TF。 • DF:方向标志,控制串操作指令。如果DF=0,则串操作过程中地址会不断增值;如果DF=1,则串操作过程中地址会不断减值; • IF:中断标志,控制可屏蔽中断。如果IF=0,则CPU不能对可屏蔽中断请求作出响应;如果IF=1,则CPU可以响应可屏蔽中断请求。 • TF:跟踪标志,如果TF=1,则CPU按跟踪方式执行指令。 • 这些控制标志一旦设置之后,便对后面的操作产生控制作用。 • 4.2.2 总线接口部件BIU • 总线接口部件的功能是负责与存储器、I/O端口传送数据。具体讲,总线接口部件要从内存取指令送到指令队列;CPU执行指令时,总线接口部件要配合执行部件从指定的内存单元或外设端口中取数据,将数据传送给执行部件,或者把执行部件的操作结果传送到指定的内存单元或外设端口中。 • 总线接口部件由下列个部分组成: • 4个段地址寄存器,即CS、DS、ES、SS; • 16位的指令指针寄存器IP; • 20位的地址加法器; • 6字节的指令队列;

第4章16位微处理器 • 说明: • 8086的指令队列为6个字节,8088的指令队列为4个字节。取指过程和指令执行过程重叠进行。 • 地址加法器用来根据16位寄存器提供的信息计算出20位的物理地址。8086可用20位地址寻址1M字节的内存空间。 • 总线接口部件和执行部件的动作管理: • 每当8086的指令队列中有2个空字节或8088的指令队列中有1个空字节时,总线接口部件就会自动把指令取到指令队列中。 • 每当执行部件准备执行一条指令时,它会从总线接口部件的指令队列前部取出指令的代码,然后用几个时钟周期去执行指令。在执行指令的过程中,如果必须访问存储器或者I/O设备,那么EU就会请求BIU进入总线周期去完成访问存储器或者I/O设备的操作;如果此时BIU正好处于空闲状态,就会立即响应EU的总线请求,如果此时BIU正在进行取指令操作,那么BIU首先完成取指令操作,然后再去响应EU发出的访问总线的请求。 • 当指令队列已满,而且EU对BIU又没有总线访问请求时,BIU便进入空闲状态 • 在执行转移指令、调用指令和返回指令时,下面要执行的指令就不是顺序排列的那条指令了,这时指令队列中已经装入的字节就没有用了。此时,指令队列中的原有内容被自动清除,BIU会接着往指令队列中装入另一个程序段中的指令。

第4章16位微处理器 • 4.2.3 存储器结构 • 8086/8088系统中存储器按字节编址,可寻址的存储器空间为1MB。

第4章16位微处理器 • 4.2.3 存储器结构 • 存储器的分段: • 8086/8088系统把1M存储空间分成若干个逻辑段,每个逻辑段容量≤64KB。 • 逻辑段可以在存储空间中浮动,段与段之间可以重叠。 • 16字节的存储空间称为1节,要求各个逻辑段从节的整数边界开始,即段首地址低4位是0,因此就把段首地址的高16位称为“段基址”,存放在段寄存器中,段内的“偏移地址” 放在IP或SP中。 • 存储器中的逻辑地址和物理地址: • 逻辑地址:由段基址和偏移地址构成,16位。 • 物理地址:实际地址、绝对地址,20位。 • 程序用逻辑地址编址,而不是用物理地址。 • 逻辑地址到物理地址的转换(由BIU中的地址加法器实现): 物理地址=段基址×16+段内偏移地址 例如:CS=2000H,IP=2200H,则物理地址=22200H • 4个段寄存器分别指向4个现行可寻址的分段的起始字节单元。一般指令程序存放在代码段中,段地址来源于代码段寄存器,偏移地址来源于指令指针IP。当涉及到一个堆栈操作时,段地址寄存器为SS,偏移地址来源于栈指针寄存器SP。当涉及到一个操作数时,则DS或ES作为段寄存器,而偏移地址为16位偏移量,该偏移量取决于指令的寻址方式。

习题 一、填空题 1、8086/8088CPU内部结构按功能分为两部分,即和。 2、CPU中的总线接口部件BIU,根据执行部件EU的要求,完成与或的数据传送。 3、8086中的BIU由个位段寄存器、一个位指令指针、字节指令队列、位地址加法器和控制电路组成。 4、8086/8088的执行部件EU由个通用寄存器、个专用寄存器、一个标志寄存器 和等构成。 5、根据功能不同,8086的标志位可分为标志和标志。 6、物理地址是指实际的位主存单元地址,每个存储单元对应唯一的物理地址,其范围是————。 7、8086/8088的状态标志有个,控制标志有个。 二、是非判断题 1、8086/8088标志寄存器共有16位,每一位都有含义。( ) 2、8086/8088的逻辑段不允许段的重叠和交叉。( ) 3、8086/8088的数据总线都是16位。( ) 4、执行转移、调用和返回指令时,指令队列中的原内容不会被清除。( ) 5、8086与8088在软件上不一定完全兼容。( )