Synchronization

Synchronization. Explicit synchronization among processes is needed to ensure a specific execution order of their operations. Three types of synchronization Mutual exclusion : access to a critical code region is restricted Point-to-point events :

Synchronization

E N D

Presentation Transcript

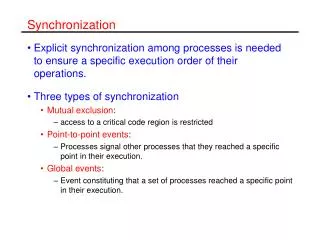

Synchronization • Explicit synchronization among processes is needed to ensure a specific execution order of their operations. • Three types of synchronization • Mutual exclusion: • access to a critical code region is restricted • Point-to-point events: • Processes signal other processes that they reached a specific point in their execution. • Global events: • Event constituting that a set of processes reached a specific point in their execution.

Components of a Synchronization Event • Acquire method • a method by which a process tries to acquire the right to the synchronization, e.g. to enter a critical section or to proceed past the event synchronization point. • Waiting algorithm • a method by which a process waits for a synchronization • Release method • a method for a process to enable other processes to proceed past a synchronization event.

Waiting Algorithms • Busy-waiting: spins for a variable to change • Blocking: suspends and is released by the OS • Trade-offs: • Blocking has higher overhead due to OS involvement • Blocking frees the processor • Busy-waiting consumes memory bandwidth while waiting • Hybrid waiting strategies combine both approaches.

Mutual Exclusion - Locks • Hardware locks • Special bus lines for locks: holding a line means holding lock • Hardware locks were mainly used for implementing higher-level software locks in memory. • Simple software lock lock: ld register, location //copy location to register cmp register, #0 //compare with 0 bnz lock //if not 0, try again st location, #1 //store 1 into location ret //return to caller unlock: st location, #0 //write 0 to location ret //return to caller

Locking with Atomic Test&Set Operation • Atomic Test&Set operations do not allow intervening accesses to the same location. • It loads the location content into a register and assigns a 1 to the location. lock: t&s register, location //copy location to register //and assign 1 to location bnz register, lock //compare old value with 0 ret //return to caller unlock: st location, #0 //write 0 to location ret //return to caller

Other Atomic Operations • Compare&swap: • Exchanges the value in location with the value in a register • Fetch&op: • Fetches the value from the location and writes the value obtained by applying the operation, e.g. fetch&increment, fetch&add

Bus Traffic is critical X X X P1 P2 P3 T&S lock T&S lock T&S lock Cache Cache Cache Memory Load exclusivecopy

Test-and-Test-and-Set • Improvement: • Test-and-Test&set lock: • Processes first test lock value with normal load • If value is 0, a test&set operation is applied to obtain the lock.

Performance Goals for Locks • Low latency • Low traffic • Scalability • Low storage overhead • Fairness

Load-Locked, Store-Conditional • Sequence of two operations • Load-lock: load the value of a location into a register • Store-conditional: writes a value to the location if this was not written in between • Advantage • No bus-traffic during waiting and no invalidations if lock could not be obtained (i.e. a failed store conditional). lock: ll reg1, location //load-lock the location bnz reg1,lock //if locked, wait sc location, reg2 //store reg2 conditionally beqz lock //wait if operation was not //successful ret //return to caller unlock: st location, #0 //write 0 to location ret //return to caller

Fair Locking - Ticket Lock A process performs two phases to obtain a lock: • Obtain a unique ticket from ticket counter (fetch&increment) • Wait for the ticket number in lock counter (normal load) A process releases a lock by incrementing the lock counter. • The locking algorithm is fair: every process will eventually obtain the lock. • The locking algorithm generates very little bus traffic.

Array-based locking: Avoids Bus Traffic on Release • Each lock is implemented by an array of p cache lines, where p is the number of processors. A process obtains a lock by • Obtaining a position in the lock array (fetch&increment) • Waiting for a release marked via an assignment to this cache line A process releases a lock by • Assigning a value to the next position in the lock array.

Point-to-Point Event Synchronization P0 P0 P1 P1 Assume intial value of A and flag is 0 Assume intial value of A and flag is 0 while (flag==0);print A; print A; A=1;flag=1; A=1; • Event synchronization can be implemented in software by busy waiting on ordinary variables. • Hardware support: Locations with Full-Empty Bit • A process can write the location only if the bit signals empty and sets it to full. • A process can read the location only if the bit signals full and sets it to empty. • Hardware supports simple producer-consumer relationships.

Global (Barrier) Event Synchronization • Centralized software implementation • struct bar_type { int counter; struct lock_type lock; int flag=0;} bar_name; • Barrier (bar_name,p){ • lock(bar_name.lock);if (bar_name.counter==0) bar_name.flag=0; //reset flag if first to reachmycount=bar_name.counter++; //mycount is private variableunlock(bar_name.lock);if (mycount==p){ //last to arrive? bar_name.counter=0; //reset counter for next bar bar_name.flag=1; //release waiting processes} else while (bar_name.flag==0){};//busy-wait for release • }

Hardware Barriers • Synchronization bus • Barrier is simply a wired-AND of lines • A processor sets its input high when it reaches the barrier and waits until the output goes high. • Advantage if barriers are executed frequently, e.g. automatic parallelization • Complications: • Synchronization among subgroup of processors • Migration of processes • Multiple processes on a single processor

Synchronization Summary • Some bus-based machines have provided full hardware support for synchronization. • Limited flexibility leads to support only simple atomic operations in hardware. • Higher-level primitives can easily be built on top of those. • Synchronization primitives are supported by libraries.