内容回顾 - 基本概念

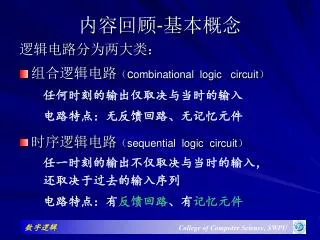

内容回顾 - 基本概念. 逻辑电路分为两大类: 组合逻辑电路 ( c ombinational logic circuit) 时序逻辑电路 ( sequential logic circuit). 任何时刻的输出仅取决与当时的输入. 电路特点:无反馈回路、无记忆元件. 任一时刻的输出不仅取决与当时的输入, 还取决于过去的输入序列. 电路特点:有 反馈回路 、有 记忆元件. 内容回顾 - 锁存器与触发器. 锁存器( Latch) 根据输入,直接改变其输出(无使能端) 有使能端时,在时钟信号的有效电平之内都可根据数据直接改变其输出状态

内容回顾 - 基本概念

E N D

Presentation Transcript

内容回顾-基本概念 逻辑电路分为两大类: • 组合逻辑电路(combinational logic circuit) • 时序逻辑电路(sequential logic circuit) 任何时刻的输出仅取决与当时的输入 电路特点:无反馈回路、无记忆元件 任一时刻的输出不仅取决与当时的输入, 还取决于过去的输入序列 电路特点:有反馈回路、有记忆元件

内容回顾-锁存器与触发器 • 锁存器(Latch) • 根据输入,直接改变其输出(无使能端) • 有使能端时,在时钟信号的有效电平之内都可根据数据直接改变其输出状态 • 触发器(Flip-Flop,F/F) • 只在时钟信号的有效边沿改变其输出状态

状态转移真值表 reset R Q S R Qn 清0 Qn+1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 1 0 0 1 1 0* 0* 置1 QL set S 功 能 表 S R Q QL 逻辑符号 逻辑符号 0 0 0 1 1 0 1 1 维持原态 0 1 1 0 0* 0* S Q R QL S Q R Q 内容回顾-RS锁存器

数字逻辑Digital logic 主 讲 陈利学 第十一讲 时序逻辑电路设计

本讲主要内容 • RS锁存器 • D锁存器 • D触发器

S-R锁存器功能表 S_L S Q S_L R_L Q QL 1 1 1 0 0 1 0 0 维持原态 0 1 1 0 1* 1* QL R_L R 逻辑符号 S Q R Q S-R锁存器(latch) 清0 置1 不定 电路维持原态 S_L = R_L = 1 S_L = 1, R_L = 0 Q = 0, QL = 1 S_L = 0, R_L = 1 Q = 1, QL = 0 S_L = R_L = 0 Q=QL=1,不定状态

S_L S 功能表 Q C S R Q QL C 维持原态 维持原态 0 1 1 0 1* 1* 0 X X 1 0 0 1 0 1 1 1 0 1 1 1 QL R R_L 逻 辑 符 号 S C R Q Q 具有使能端的S-R锁存器 —— 又称“时钟S-R锁存器” (1) C = 0时: 维持原态 (2) C = 1时: 与S-R锁存器相似 注意:当S=R=1时,若C由10, 则下一状态不可预测。

C S R Q QL 0 X X 1 0 0 1 0 1 1 1 0 1 1 1 维持原态 维持原态 0 1 1 0 1* 1* C S R Q 时钟S-R锁存器时序图 动作特点:输入信号在时钟(使能端)有效期间,都能直接改变触发器的状态。

S D Q C QL D锁存器功能表 R C D Q QL 1 0 0 1 1 1 1 0 0 X 保持 逻辑符号 D Q C Q Q = D D锁存器 数据 输入端 控制端 ENABLE CLK、G 输出状态保持不变 C = 0, 输出随输入状态而改变 C = 1, D = 1时,Q = 1 D = 0时,Q = 0 透明锁存器

状态转移真值表 D Qn+1 0 1 0 1 D=1 D=1 D=0 0 1 D=0 D锁存器的功能描述 特征方程:Qn+1 = D(C=1) 状态图

C D Q tpLH(CQ) tpLH(DQ) tpHL(CQ) tsetup thold tpHL(DQ) 建立时间 setup time 保持时间 hold time D锁存器的时序图 在C的下降沿附近有一个时间窗 这段时间内D输入一定不能变化

D Q C Q D Q C Q D Q C Q D Q C Q DIN[3:0] WR RD DOUT[3:0] 锁存器的应用

Xi Yi Ci X Y CI S CO Si Ci+1 Xi Yi 时钟控制 X Y CI CO S Ci Ci+1 Q D Q C 暂存 Si 锁存器的应用 串行输入、串行输出 注意:时钟同步 CLK 再谈串行输入 加法器的实现

Q 亚稳态 Q_L 稳态 稳态 内容回顾 • 时序逻辑电路 • 输出取决于输入和过去状态 • 电路特点:有反馈回路、有记忆元件 • 双稳态元件 注意:亚稳态特性 0态 和 1态

R Q QL S Q Q_L 内容回顾 • 时序逻辑电路 • 输出取决于输入和过去状态 • 电路特点:有反馈回路、有记忆元件 • 双稳态元件 如何加入控制信号?? 0态 和 1态

R D Q C S-R锁存器 QL S 有约束条件 S S_L Q C QL R R_L 内容回顾 • 锁存器与触发器 S-R锁存器 具有使能端的S-R锁存器 D锁存器

CLK 触发器 正边沿 上升沿 负边沿 下降沿 只在时钟信号的边沿改变其输出状态

触发器 • 从功能上分 • D触发器、S-R触发器、J-K触发器、T触发器 • 从结构上分 • 主从结构触发器、边沿触发器 • 其他类型触发器 • 带使能端的触发器、扫描触发器 • 施密特触发器、单稳态触发器

主 master 从 slave Qm D D Q C Q D Q C Q Q QL CLK D触发器 —— 主从结构 CLK=0时, 主锁存器工作,接收输入信号 Qm = D 从锁存器不工作,输出 Q 保持不变 主锁存器不工作,Qm 保持不变 从锁存器工作,将 Qm 传送到输出端 CLK=1时,

Qm D D Q C Q D Q C Q Q QL CLK CLK D Qm Q

逻辑符号 D CLK Q QL 功 能 表 D Q CLK Q 0 0 1 1 1 0 X 0 保持 X 0 保持 表示边沿触发特性 CLK D Q

Q CLK CLK D D Q ——电平有效 D锁存器 D触发器 —— 边沿有效

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY dff IS PORT ( D : in std_logic; clk :in std_logic; Q : out std_logic ); END dff; ARCHITECTURE behavior OF dff IS BEGIN PROCESS (clk,D) BEGIN IF clk’event AND clk=‘1’ THEN Q <= D; END IF; END PROCESS; END behavior; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY latch IS PORT ( D : IN std_logic; C : IN std_logic; Q : OUT std_logic ); END latch; ARCHITECTURE behavior OF latch IS BEGIN PROCESS (D, C) BEGIN IF C = '1' THEN q <= D; END IF; END PROCESS; END behavior; Latch vs Flip-Flop

演示 • 仿真 • D:\degital_logic\my_latch_test • D:\degital_logic\my_dff_test

latch latch D D Q C Q D Q C Q Q D Q1 CLK CLK (图1) Q1 Q F / F F / F Q1 D Q CLK Q D Q CLK Q D Q (图1) CLK 触发器的应用 利用触发器作为移位寄存器(图1) 思考:能否将触发器改为锁存器