Term Project Overview

120 likes | 142 Views

Design and implement a pipelined RISC processor from scratch, adding functions like hazard detection and forwarding units. Develop an assembler to optimize code and minimize stalls. Includes task assignments for team members and specific project phases using Quartus II and UP2 board.

Term Project Overview

E N D

Presentation Transcript

Term Project Overview Yong Wang

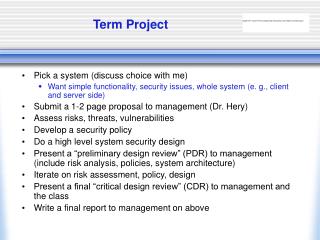

Introduction • Goal • familiarize with the design and implementation of a simple pipelined RISC processor • What to do • Build a processor from scratch (single-cycle implementation) • Add some functions • Pipeline datapath, pipeline control, hazard detection unit, forwarding unit, branch hazard handling unit • Write an assembler that detects data hazard and optimizes the code to minimize stalls

Project Assignment • Team-based work • 4 to 5 Team members • Task assignment for reference • 2-3 ISA and logical design • 1 assembler and application program • 1 project management (team leader) and website maintenance

Project Facilities • Altera UP2 education board and manual • Altera Quartus II Web Edition software (downloadable from website) • Has a retired version, MaxPlusII software • ByteBlasterMV parallel port download cable

Project Overview Input: DIP, PB Processor logical design (design, compile, simulate) Components design, compile and simulate download UP2 board Application Program in MIPS assembly Assembler in high-level language Output: displays (.mif file)

Project Phases On paper • QuartusII • Graphical tool • VHDL C, C++, Java UP2 board

Phase I Basic Design • Processor structure • 5 stage • Standard hazard handling addressed in textbooks and lectures • 4 stage or less • Eliminate some hazards and simplify hardware design • Components: PC, decoder, ALU, pipeline registers, I/O, IM, DM, etc.

Phase I Basic Design (continued) • Instruction length • ISA, refer to MIPS • How many instruction types (R, I, J) • Instruction format • Instruction and data bus width • Instruction memory (# of inst * avg. instr. length) • data memory • immediate field • register file sizes (#, and # of bits per register)

Phase II Logic Design • Components to be designed • PC • decoder • ALU • Forwarding units • Memory mapped I/O • pipeline registers (after your single cycle CPU design) • Components to be customized • IM (LPM_file, LPM_WIDTH, LPM_WIDTHAD) • A ready-to-use ROM component • DM (LPM_file, LPM_WIDTH, LPM_WIDTHAD) • A ready to use RAM component

Phase III Logical Simulation • Compile – no design errors; also check the warnings • Simulation– implements desired functions • Feed signals to inputs, run it and check the output signals • The most important debugging tool • Timing analyzer • Analyzing the system efficiency

Phase IV Assembler • Choose any high-level development language • Java, C, C++, Perl • Function requirement (can use hardware also) • Branch hazards, Load stalls • Steps • Resolve all symbols • Convert instructions to the proper memory format that Altera specifies (an example in Appendix A in project description)

Phase V Work on board • Connect to computer by ByteBlaster • Debug • Make sure your processor (and the application program) works in simulation before downloading to board