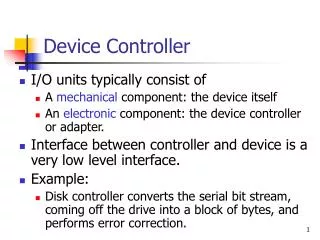

Device Controller

Device Controller. I/O units typically consist of A mechanical component: the device itself An electronic component: the device controller or adapter. Interface between controller and device is a very low level interface. Example:

Device Controller

E N D

Presentation Transcript

Device Controller • I/O units typically consist of • A mechanical component: the device itself • An electronic component: the device controller or adapter. • Interface between controller and device is a very low level interface. • Example: • Disk controller converts the serial bit stream, coming off the drive into a block of bytes, and performs error correction.

Input/ Output Problems • Wide variety of peripherals • Delivering different amounts of data • At different speeds • In different formats • All slower than CPU and RAM • External devices are not generally connected directly into the computer bus structure • Need I/ O modules • Interface to CPU and Memory • Interface to one or more peripherals

External Devices • Human readable • Screen, printer, keyboard • Machine-readable • Monitoring and control • Communication • Modem • Network Interface Card (NIC)

I/ O Module Function • Control & Timing • CPU Communication • Device Communication • Data Buffering • Error Detection

I/O Steps • CPU checks I/O module device status • I/O module returns status • If ready, CPU requests data transfer • I/O module gets data from device • I/O module transfers data to CPU • Variations for output, DMA, etc.

I/ O Module Decisions • Hide or reveal device properties to CPU • Support multiple or single device • Control device functions or leave for CPU

Input Output Techniques • Programmed • Interrupt driven • Direct Memory Access (DMA)

Programmed I/O • CPU requests I/O operation • I/O module performs operation • I/O module sets status bits • CPU checks status bits periodically • I/O module does not inform CPU directly • I/O module does not interrupt CPU • CPU must wait

I/ O Commands • CPU issues address • Identifies module (& device if >1 per module) • CPU issues command • Control - telling module what to do • e. g. spin up disk • Test - check status • e. g. power? Error? • Read/ Write • Module transfers data via buffer from/ to device • CPU is in direct control of the operation

I/O Addressing • To give a command to an I/O device, the processor must be able to address the device and supply commands • Two Methods are used to address the device • Memory mapped I/O • Isolated I/O

Memory Mapped I/O • Portions of the address space are assigned to I/O devices • i.e I/O devices and memory share a single address space • Processor treats the status and data registers of I/O module as memory locations • Reads and Writes to these locations (Registers) are interpreted as commands to the I/O device

Memory-Mapped I/O (1) (a) Separate I/O and memory space (b) Memory-mapped I/O (c) Hybrid Benefit?

Memory-Mapped I/O (2) (a) A single-bus architecture (b) A dual-bus memory architecture Benefit?

CPU Viewpoint • Issue read command • Do other work • Check for interrupt at end of each instruction cycle • If interrupted: - • Save context (registers) • Process interrupt • Fetch data & store

Isolated I/O • If the system bus is equipped with separate memory read and write, and input and output command lines, then • Command line specifies whether the address on the bus is related to a memory location or an I/O device • Can have as many I/O devices as memory locations • Because address space for I/O is isolated from memory , this approach is know as Isolated I/O

Programmed I/O: Adv. & Disadv. • Advantages of Programmed I/O • Simple to implement • Requires very little special software or hardware • Disadvantages: • Speed difference between CPU and the peripheral devices -- orders of magnitude: programmed I/O wastes an enormous amount of CPU cycles • Very inefficient • CPU slowed to the speed of the peripheral

Interrupt Driven I/O • Basic Operation • CPU issues read command • I/O module gets data from peripheral whilst CPU does other work • I/O module interrupts CPU • CPU requests data • I/O module transfers data

Interrupts • Connections between devices and interrupt controller actually use interrupt lines on the bus rather than dedicated wires

Host-controller interface: Interrupts • CPU hardware has the interrupt report line that the CPU senses after executing every instruction • device raises an interrupt • CPU catches the interrupt and saves the state (e.g., Instruction pointer) • CPU dispatches the interrupt handler • interrupt handler determines cause, services the device and clears the interrupt • Why interrupts? • Real life analogy for interrupt • An alarm sets off when the food/laundry is ready • So you can do other things in between

Support for Interrupts • Need the ability to defer interrupt handling during critical processing • Need efficient way to dispatch the proper device • Interrupt comes with an address (offset in interrupt vector) that selects a specific interrupt handling • Need multilevel interrupts - interrupt priority level

Interrupt Handler • At boot time, OS probes the hardware buses to • determine what devices are present • install corresponding interrupt handlers into the interrupt vector • During I/O interrupt, controller signals that device is ready

Direct Memory Access • Interrupt driven and programmed I/ O require active CPU intervention • Transfer rate is limited • CPU is tied up • DMA is the answer • DMA takes the CPU out of the I/ O task except for initialization • Large amounts of data can be transferred between memory and the peripheral without severely impacting CPU performance

Function and Operation • DMA Function • Additional Module (hardware) on bus • DMA controller takes over from CPU for I/ O • DMA Operation • CPU tells DMA controller: - • Read/ Write • Device address • Starting address of memory block for data • Amount of data to be transferred • CPU carries on with other work • DMA controller deals with transfer • DMA controller sends interrupt when finished

DMA Transfer - Cycle Stealing • DMA controller takes over bus for a cycle • Transfer of one word of data • Not an interrupt • CPU does not switch context • CPU suspended just before it accesses bus • i. e. before an operand or data fetch or a data write • Slows down CPU but not as much as CPU doing transfer

DMA Configurations (1) • Single Bus, Detached DMA controller • Each transfer uses bus twice • I/O to DMA then DMA to memory • CPU is suspended twice DMA Controller I/O Device I/O Device Main Memory CPU

DMA Configurations (2) DMA Controller DMA Controller Main Memory • Single Bus, Integrated DMA controller • Controller may support >1 device • Each transfer uses bus once • DMA to memory • CPU is suspended once CPU I/O Device I/O Device I/O Device

DMA Configurations (3) DMA Controller Main Memory CPU • Separate I/O Bus • Bus supports all DMA enabled devices • Each transfer uses bus once • DMA to memory • CPU is suspended once I/O Device I/O Device I/O Device I/O Device

Direct Memory Access (DMA) • Direct memory access (DMA) • Assists in exchange of data between CPU and I/O controller • CPU can request data from I/O controller byte by byte – but this might be inefficient (e.g. for disk data transfer) • Uses a special purpose processor, called a DMA controller

DMA-CPU Protocol • Use disk DMA as an example • CPU programs DMA controller, sets registers to specify source/destination addresses, byte count and control information (e.g., read/write) and goes on with other work • DMA controller proceeds to operate the memory bus directly without help of main CPU – request from I/O controller to move data to memory • Disk controller transfers data to main memory • Disk controller acks transfer to DMA controller

Direct Memory Access (DMA) • Operation of a DMA transfer

DMA Issues • Handshaking between DMA controller and the device controller • Cycle stealing • DMA controller takes away CPU cycles when it uses CPU memory bus, hence blocks the CPU from accessing the memory • In general DMA controller improves the total system performance

Discussion • Tradeoffs between • Programmed I/O • Interrupt-driven I/O • I/O using DMA • Which one is the fastest for a single I/O request? • Which one gives the highest throughput?