Efficient Bubonic Assembly Language Development for CS232 Computer Architecture

180 likes | 270 Views

Explore the features, instruction set, development process, datapath, and testing of the Bubonic Assembly Language developed by Team R. The language boasts special features like memory copy instructions and a standalone return address register. Discover the challenges faced during development and the innovative solutions implemented.

Efficient Bubonic Assembly Language Development for CS232 Computer Architecture

E N D

Presentation Transcript

Bubonic Assembly Language CS232 Computer Architecture I – Team R Douglas Jeffries Himanshu Narayana David Rickard February 13, 2002

Overview • Special Features • Instruction Set • Development • Datapath • Control • Testing • Demonstration

Special Features • Memory copy instruction • Direct copy between memory locations • Return address register is standalone • Special instructions to load and store • Assembler • Easy assembly of code • Effort to write assembler paid off • Assembled ~100 programs for testing

Instruction Set • 30 instructions designed • 28 instructions implemented • Not enough time for mult or div • 2 instructions “borrow” opcodes • Needed more opcodes • Not really pseudo-instructions • Have their own datapath and control

Instruction Set • Arithmetic • add, sub • Planned mult, div • Logical • and, or, xor, nand, nor, xnor, slt • andi, ori • sll, srl • Branch • beq, bne

Instruction Set • Register • copy, swap, lui • swra, lwra • Memory • lw, sw, mtm • Jump • j, jr, jal, jm, jra

Development • Website documenting progress • Includes all documentation • Progressive datapath construction • Used for design, implementation, testing • Groups of instructions at each step • Test cases • Ensure soundness of design • Include obscure and uncommon cases

Development Problems • Xilinx state diagram and Verilog • Spent over a week attempting to fix it • Advised to use ABEL instead

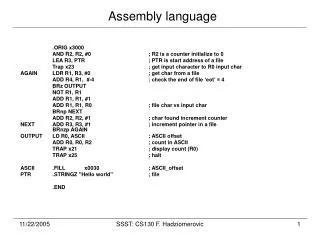

Datapath • 16-bit memory addresses • 16-bit data bus • 8 registers in register file • 7 static registers • PC, IR, RA, MDR, ALUOut, A, B

Register Name Save Type Description 0 $zero - Value is always zero. 1 $t0 caller Temporary 2 $t1 caller Temporary 3 $t2 caller Temporary 4 $s0 callee Preserved across function calls 5 $s1 callee Preserved across function calls 6 $v caller Return value 7 $sp callee Stack pointer Register File

Testing • 104 proposed test cases • Make sure basic instructions work first • Cannot test every value, so go for exceptions and extremes • Assembler to speed up process • Easy implementation of new programs

Xilinx Implementation • Implementation on 4010XLPC84 • Did not fit on device (179% of CLBs) • 719 / 400 CLBs • 128 32x1 RAMs • 1170 4-in LUTs • 360 3-in LUTs • 128 / 880 Bounded IOBs

Xilinx Implementation • Implementation on 4028XLHQ240-09 • We picked this device at random • Device usage • 827 / 1024 CLBs • 229 / 2048 CLB flip flops • 1426 / 2048 4-in LUTs • 488 / 1024 3-in LUTs • 128 / 2176 TBUFs • 34 / 193 External IOBs

Implementation Speed • Minimum period of 101.497 ns • Maximum net delay of 29.230 ns • Clock speed of 9.853 MHz

Future Improvements • Implement multiplication and division • Multiple input file support for assembler • Better pseudo-instruction substitutions by assembler