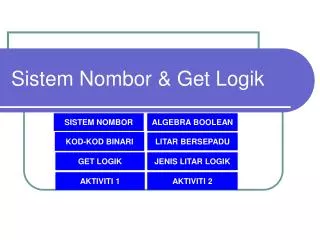

Sistem Nombor & Get Logik

500 likes | 1.49k Views

Sistem Nombor & Get Logik. SISTEM NOMBOR. ALGEBRA BOOLEAN. KOD-KOD BINARI. LITAR BERSEPADU. GET LOGIK. JENIS LITAR LOGIK. AKTIVITI 1. AKTIVITI 2. GET LOGIK. Logik dalam sistem Binari digunakan untuk menyatakan proses dan operasi sesuatu maklumat Binari dari segi penyataan matematik!

Sistem Nombor & Get Logik

E N D

Presentation Transcript

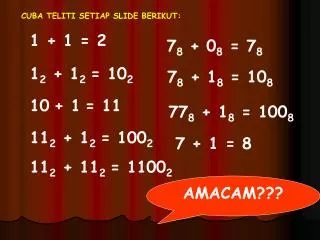

Sistem Nombor & Get Logik SISTEM NOMBOR ALGEBRA BOOLEAN KOD-KOD BINARI LITAR BERSEPADU GET LOGIK JENIS LITAR LOGIK AKTIVITI 1 AKTIVITI 2

GET LOGIK • Logik dalam sistem Binari digunakan untuk menyatakan proses dan operasi sesuatu maklumat Binari dari segi penyataan matematik! • Logik Binari terdiri pembolehubah Binari dan juga ‘operasi logik’. • Operasi ini memerlukan get-get logik.

Simbol Jadual kebenaran A B C 0 0 0 0 1 0 1 0 0 1 1 1 Formula C = A.B @ C = A x B Get DAN A C B

Simbol Jadual kebenaran A B C 0 0 0 0 1 1 1 0 1 1 1 1 Formula C = A + B Get ATAU A C B

Get TAK Simbol Jadual kebenaran A C 0 1 1 0 Formula C = A

Simbol Jadual kebenaran A B C 0 0 1 0 1 1 1 0 1 1 1 0 Formula C = A . B Get TAK DAN A C B

Simbol Jadual kebenaran A B C 0 0 1 0 1 0 1 0 0 1 1 0 Formula C = A +B Get TAK ATAU A C B

Simbol Jadual kebenaran A B C 0 0 0 0 1 1 1 0 1 1 1 0 Formula C = A . B + A . B = A B Get Eksklusif ATAU A C B

Simbol Jadual kebenaran A B C 0 0 1 0 1 0 1 0 0 1 1 1 Formula C = A . B + A . B = A B Get Eksklusif TAK ATAU A C B

Aktiviti 1 A. Membina dan menguji litar logik Peralatan dan Bahan

Aktiviti 1 Langkah kerja Sambung litar seperti di bawah pada papan projek :- 74LS08 – GET ? R = 150Ω 1 S1-B 1 0 S2-A 0

Aktiviti 1 Letakkan kedudukan suis ikut kombinasi seperti jadual keputusan di bawah :- Catat semua keadaan keluaran dengan :- Sentuh kuar logik ke pin 3; Sentuh kuar osiloskop ke pin 3, set pada voltan/masa ke 5 V/div

Aktiviti 1 Perbincangan Apakah keadaan LED apabila keluaran berada pada logik 1. Berapakah voltan yang mewakili logik 1. Kesimpulan Dari ujikaji, apakah get pada litar bersepadu 74LS08.

Litar-litar Logik • Litar logik digital terdiri daripada 2 kategori iaitu: • Litar logik gabungan (COMBINATIONAL) • Litar logik jujukan (SEQUENTIAL)

Litar logik gabungan • Gabungan get-get logik asas untuk menentukan nilai keluaran secara terus oleh nilai masukan. • Untuk mereka litar logik gabungan, perlukan pengetahuan tentang:- • Sistem nombor perduaan (sistem digital) • Perlaksanaan suatu rangkap kepada litar logik • Jadual benar • Pemudahan rangkap (Karnaugh-Map) • Apabila semua ilmu tersebut deketahui, litar bagi sesuatu sistem boleh direka!

Litar logik gabungan • Beberapa jenis litar logik gabungan yang digunakan sumber alamat dalam ingatan:- • Pengkod (Encoder) • Penyahkod (Decoder) • Pemultipleks (Multiplexer) • Nyahmultipleks (Demultiplexer) • Pembanding (Comparator) • Penambah-Penuh (Full-Adder)

Penyahkod • Digunakan untuk menukar beberapa kod seperti binari, hex dan BCD kepada nilai numeric (angka sebenar). • Litar bersepadu 74LS47 adalah contoh penyahkod BCD ke decimal. • Digabungkan dengan mengunakan keluaran yang diperlukan serta algebra boolean (K-Map, De Morgan)

Litar Bersepadu (Integrated Circuit) • Cip Litar Bersepadu (IC Chip) terbahagi kepada beberapa jenis, berdasarkan bilangan get-get di dalamnya:- • SSI (Smal Scale Integration), mengandungi kurang daripada 12 get-get asas per cip • MSI (Medium Scale Integration), mengandungi 12 - 99 get-get asas per cip • LSI (Large Scale Integration), mengandungi 100 - 999 get-get asas per cip • VLSI (Very Large Scale Integration) mengandungi 10,000 - 99,999 get-get asas per cip • ULSI (Ultra Large Scale Integration), mengandungi lebih 100,000 get-get asas per cip

Litar Bersepadu • Keluarga Litar Bersepadu (IC Chip) yang utama terbahagi kepada 2 iaitu :- • Bipolar Junction Transistor (BJT) • TTL • ECL • Metal Oxide Semiconductor (MOS) – drp FET • PMOS • NMOS • CMOS

Litar Bersepadu • TTL (transistor-transistor logic) – yang merujuk kepada penggunaan BJT dalam pembinaannya. • Ada beberapa jenis TTL iaitu; standard TTL, low-power TTL, Schottky TTL, low-power Schottky TTL, advanced low-power Schottky TTL, advanced Schottky TTL. • CMOS (complementary metal oxide semiconductor) – merujuk kepada penggunaan PMOS dan NMOS dalam pembinaannya. • Sesuatu cip yang dibina dengan menggunakan TTL dan CMOS akan menjalankan fungsi dan operasi yang sama. Yang membezakannya hanyalah ciri prestasinya (performance characteristic).

Algebra Boolean • Boolean Algebra adalah pernyataan matematik bagi sistem digit. • Penting untuk tujuan pemahaman dan analisis litar sistem digit.

Algebra Boolean • Hukum 1. Hukum Tukar-tertib (Commutative Laws) ABC = ACB = CBA A+B+C = B+C+A = C+A+B 2. Hukum Sekutuan (Associative Laws) A+(B+C) = (A+B)+C A(BC) = (AB)C 3. Hukum Taburan (Distributive Laws) A(B+C) = AB+AC

Permudah rangkap Boolean Pemudahan boleh dilakukan dengan menggunakan hukum-hukum dan teori asas Boolean. Cth; F = (A + B)(A + B) = AA + AB + AB +BB = A + AB + AB + 0 = A (1 + B) + AB = A + AB = A (1+B) = A

Ungkapan Boolean • Ungkapan Boolean digunakan untuk menganalisis fungsi litar-litar digit. • Terdapat dalam 2 bentuk iaitu : • Jumlah hasil darab (Sum of Product, SOP) • Hasil darab jumlah (Product of Sum, POS)

SOP(jumlah hasil darab) • Gabungan litar get DAN(hasil darab) dan ATAU(jumlah) • Contoh Y = AB + CD A B Y C D

POS(hasil darab jumlah) • Gabungan litar get ATAU(jumlah) dan DAN(hasil darab) • Contoh Y = (A + B)(C + D) A B Y C D

Litar logik jujukan • Mempunyai fungsi ingatan • Nilai keluaran bergantung kepada nilai masukan dan juga nilai pada ingatan (nilai keluaran sebelumnya)

Litar logik jujukan • Sistem logik jujukan berasaskan beberapa komponen litar jujukan yang dikenali sebagai flip-flops. • Flip-flop yang paling asas digunakan adalah flip-flop RS (Set-Reset). • Antara flip-flop lain yang digunakan adalah JK, D dan T

Flip-Flop RS Simbol Tatarajah S Q Get TAK DAN S Q Q R R Q S Q Get TAK ATAU Q R

Flip-Flop RS Jadual Kebenaran Flip Flop RS Get TAK ATAU S Q Get TAK ATAU Q R Jadual Kebenaran Flip Flop RS Get TAK DAN S Q Get TAK DAN Q R

Flip-Flop RS Denyut Simbol Dengan tambahan denyut (clock), keluaran bergantung kepada picuan +ve atau picuan –ve denyut Tatarajah S Q S Q Clock Q R Clock Q R

Masukan Keluaran Status S R Clock Q Q 0 0 X Q0 Q0 No change 0 1 0 1 Reset 1 0 1 0 Set 1 1 ? ? Invalid Q Flip-Flop RS Denyut Jadual Kebenaran Flip Flop RS Denyut Picuan +ve Gelombang masukan & keluaran mengikut denyut +ve Clock 1 2 3 4 5 6 S R No change Reset Reset Q Set Set Set

Litar logik jujukan • Litar Jujukan berdasarkan kepada penggunaan flip-flop adalah seperti :- • Penghitung (Counter) • Shift Register • Memory Device • Pemasa (Timer 555)

Penghitung (Counter) • Menyimpan ingatan (memory) sebelum menyimpan maklumat yang baru ikut denyut (Clock) yang dihasil. • Terdiri dari gabungan flip-flop JK dan get-get logik (Adder). • Penghitung yang selalu digunakan adalah Penghitung 4-bit. 74LS90 A B RO(1) RO(2) QA QD Vcc Gnd R9(1) QB R9(2) QC Gambarajah Litar Bersepadu

Pemasa (Timer 555) • Digunakan untuk menghasilkan rantaian denyut yang serupa @ sama • Menggunakan flip-flop jenis RS. • Dapat memberi picuan yang sama kepada penghitung (counter), pengeluar bunyi, penguji keterusan dan pembilang getar (multivibrator). Gnd 1 Vcc Trigger Discharge 555 Output Threshhold Reset Control Voltage Gambarajah Litar Bersepadu

Aktiviti 2 • Membina litar berdigit yang mengandungi pemasa, penghitung, penyahkod dan pemapar. Sambung litar seperti rajah di bawah :- a 1 b c d 74LS47 74LS90 e f 555 g

Aktiviti 2 Perbincangan Dari litar yang dibina, namakan komponen yang termasuk dalam kategori litar logik berkombinasi.