Implementing Constructive Synchronous Programs on POLIS CFSM Networks

Explore constructive synchronous programs on POLIS CFSM networks, emphasizing compositionality. Study synchronization principles, practical implementations, well-behaved networks, and optimization techniques. The use of synchronous digital circuits for deterministic and concurrent operations is discussed, with a focus on implementing synchronous languages effectively. The text outlines methodologies, formal semantics, and previous research for running large-scale programs on CFSM networks, considering progressive relaxation of synchrony. Theoretical content is presented through constructive logic, Boolean circuits, and network propagation concepts. The application of POLIS as a GALS model for hardware/software codesign is examined, highlighting the feasibility of synchronous language implementation on CFSM networks.

Implementing Constructive Synchronous Programs on POLIS CFSM Networks

E N D

Presentation Transcript

Implementing Constructive Synchronous Programs on POLIS CFSM Networks G.Berry E.Sentovich Ecole des Mines de Paris / INRIA Cadence Berkeley Labs

Concurrency :The Compositionality Principle Q R P P || Q

d t t’ Q R P t’’ t’’ = t + d + t’ t’’ ~ t ~ d ~ t’ t ~ t + t

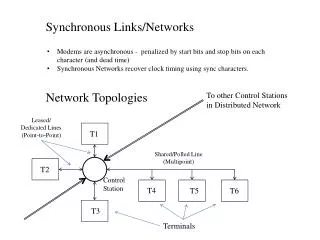

3 principalsolutions : • t arbitrary asynchrony • t = 0 synchrony • t fixed or bounded propagation

_ + Cl H t arbitrary : Brownian Motion _ + + H Cl _ HCL H Cl + _ H HCL Cl + HCL H Chemical reaction Internet Routing HCL +

t = 0 : Perfect Synchrony Synchronous = zero delay Communication by instantaneous broadcast Concurrency + determinism Reference: Newtonian Mechanics

T fixed or bounded : Vibration • Propagation of • Sound • Light • Heat • Wind

Synchronous Digital Circuits REQ OK PASS TRY GO GET_TOKEN PASS_TOKEN OK=REQandGO PASS= not REQandGO GO=TRYorGET_TOKEN PASS_TOKEN= reg(GET_TOKEN)

Synchronous view : magicallysolve equations 0-delay Vibration view : propagate voltages speed of light Acyclic circuits : stabilization in predictable time Wait long enough, same result as 0-delay !

module Sender : type Message input MESSAGE : Message; output SEND : Message, SENT; input MS, ACK; loop await MESSAGE; abort every 100 MS do emit SEND (?MESSAGE) end every when ACK; emit SENT end loop end module

POLIS : a GALS model Globally Asynchronous Locally Synchronous CFSM Input buffer

CFSM Input Buffer = presence + value - A CFSM is runnable when an input comes in - Several inputs may come in before actual run - Presence/ absence can be tested for each input - Value can be accessed for present signals - Transition in 0-delay - Output broadcast by the network, with delay - 1-place buffers can be overwritten

Synchronous programs • nice semantics / mathematics • concurrency + deterministic • optimization + verification feasible • limited in scope: compact systems • CFSM networks • POLIS implementation model • good for hardware / software codesign • formal semantics, but can be wild • semanticspurely operational(scheduler)

Can we implement synchronous languages on CFSM networks? • Run large-scale synchronous programs on networks • Study classes of “well-behaved” CFSM networks • Study progressive relaxation of synchrony • Previous work : P. Caspi and A. Girault • E,. Ledinot et.al., Dassault Aviation

Constructive Circuits Esterel -> circuits, combinational cycles allowed 3 kinds of cyclic circuits: - Well-behaved X = I and Y Y = not I and X - Outlaws X = X X = not X X I Y

Strange Circuits ToBe = ToBe or not ToBe ToBe Unique Boolean solution No electrical stabilization for some delays Electrons cannot reason by contradiction => Constructive Boolean Logic

E=0 F=0 E=1 F=1 E and F = 0 E and F = 0 E and F = 1 E=0 E=1 not E = 1 not E = 0 X=E E=b X=b Constructive Boolean Logic Fact : E=0 or E=1 E or not E = 1not provable unless E=0 or E=1 FACTS!NO GUESS!

Running Example I X Y J X = I and not Y Y = J andnot X OK unless I = J = 1

X = I and not Y Y = J and not X Proofs (1) I=0 (2) J=1 (3) X=0 from (1) (4) not X=1 from (3) (5) Y=1 from (2) and (4) (1) I=1 (2) J=0 (3) Y=0 from (2) (4) not Y=1 from (3) (5) X=1 from (2) and (4) Topological ordering : data independent Proof ordering : data dependent No proof of X and Y if I=J=1

Theorem (Berry-Shiple) : equivalence of 3 views • Constructive semantics • convergence = provability of a fact for each wire • Delay-independent electrical behavior • convergence = stabilization for any • delay assignment • Scott’s denotational semantics - 3-valued logic • solve equation by least fixpoint in { , 0, 1} • convergence = all wire values in {0,1} • => compositionality T

X = I and not Y Y = J and not X Esterel v5 Algorithm I=0 . J=1 X : 2 Y : 2 I=0. J=1 . X=0 X : 1 Y : 2 I=0 . J=1 . X=0 X : 1 Y : 1 I=0 . J=1 .X=0X : 1 Y : 0 I=0 . J=1 . X=0 . Y=1 X : 1 Y : 0 I=0 . J=1 . X=0 . Y=1 X : 0 Y : 0

X = I and not Y Y = J and not X Esterel v5 Algo. I=0 . J=0 X : 2 Y : 2 I=0. J=0 . X=0 X : 1 Y : 2 I=0 . J=0 . X=0 . Y=0 X : 1 Y : 1 I=0 . J=0 .X=0 . Y=0 X : 1 Y : 0 I=0 . J=0 . X=0 .Y=0X : 0 Y : 0

POLIS Implementation • Encode facts in CFSM events • Use one CFSM per gate • Use the network to propagate the facts Combinational gates -> sequential CFSMs Synchronous cycle -> full network execution

Constructive and not gate as a CFSM - v1 A C B input A: boolean, B : boolean; output C : boolean; [ await A; if not ?A then emit C(false) end || await B; if ?B then emit C(false) end ]; if ?A and not ?B then emit C(true) end

V2 : protecting double emission signal Caux : combine boolean with and in [ await A; if not ?A then emit Caux(false) end || await B; if ?B then emit Caux(false) end ]; if ?A and not ?B then emit Caux(true) end || await Caux; emit C(?Caux) end signal

Given an input assignment, the network builds a proof • Each gate buffer is written at most once • - no buffer overwriting • - bounded time (linear) • Termination when no more runnable CFSM • - #events = #fanins -> constructive • - else non-constructive • Any scheduling gives the right answer!

But works only for one global tick! Macro-cycles - give synchronous events successively - logical timing by stream ordering a0 a1 a2 a3 a4 b0 b1 b2 b3 b4 c0 c1 c2 c3 c4

Four basic solutions : 1. Waitlong enough (as for circuits) 2. Compute explicit termination signal 3. Let the scheduler report termination 4. Use a flow control protocol -> pipelining

Flow Control A_Free A C B C_Free B_Free

V3 : flow control loop signal Caux : combine boolean with and in [ await A; emit A_Free; if not ?A then emit Caux(false) end || await B; emit B_Free; if ?B then emit Caux(false) end ]; if ?A and not ?B then emit Caux(true) end || [ await Caux || await C_Free ] ; emit C(?Caux) end signal end loop

Automatic Gate Reset A gate resets for next tick when it has received all its input. No additional protocol needed! A=0 A_Free C_Free C=0 B=1 B_Free loop A=1 A_Free C_Free B=1 B_Free C=1 loop

Pipelining Problem : out-of-order data for next cycle A(0) -> A_Free C_Free -> C(0) A(1)-> B(1) -> B_Free 1. Memorize A(1) in the CFSM - heavy! 2. Write back 1 in the A buffer but gate immediately made runnable again! 3. Tell the scheduler that only arrival of B matters => sensitivity lists

module AndNot : % Boolean IO input A : boolean, B : boolean; output X : boolean; % Flow control IO output A_Free, B_Free; input C_Free; % Scheduling IO output A_Wait, B_Wait; output C_Free_Wait;

loop signal Caux : combine boolean with and in < handle A and B > || <handle C > end signal end loop

[ abort sustain A_Wait when A; emit A_Free; if not ?A then emit Caux(false) end || abort sustain B_Wait when B; emit B_Free; if ?B then emit Caux(false) end ]; if ?A and not ?B then emit Caux(true)

[ await Caux || abort sustain C_Free_Wait when C_Free ]; emit C(?Caux)

Temporary Summary • One can implement a constructive circuit in POLIS • by translating each gate into a CFSM • Therefore, on can implement Esterel by first • translating Esterel programs into gates • Of course, this is inefficient : too fine grain • But, we did not use compositionality yet!

Using Compositionality • Any network of gates acts just as a gate • Group gates either synchronously, using v5 algo., • or asynchronously, in the network • Adjust grouping according to geographical • and performance requirements

X=0 Y=1 Optimisation • Group messages going from A to B • Precompute the transitive effect of messages X=0 Y=1

Summary • Constructive logic semantics • facts as information quanta • Propagate facts • synchronously in CFSM nodes • asynchronously in the network • Correct by construction • Applicable to (some) real problems • A step to mixed 0-delay / vibration • language design

Termination signal I X Y J DONE Too expensive Non-local