MPSoC Programming Solution

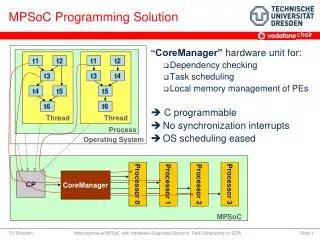

This document presents a detailed overview of the CoreManager hardware unit for dynamic task scheduling in heterogeneous MPSoCs. It focuses on dependency checking, local memory management, and programmable C features that enhance processing efficiency without synchronization interrupts. The system, implemented on a Tomahawk platform, optimizes baseband signal processing tasks, addressing the key challenges of scalability and power consumption. Evaluation of software and hardware scheduling performance highlights significant speed-up potential, empowering advanced applications in Software Defined Radio (SDR).

MPSoC Programming Solution

E N D

Presentation Transcript

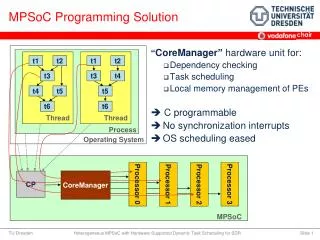

MPSoC Programming Solution OperatingSystem “CoreManager” hardware unit for: • Dependency checking • Task scheduling • Local memory management of PEs C programmable No synchronization interrupts OS scheduling eased Process Thread Thread t1 t2 t1 t2 t3 t3 t4 t4 t5 t5 t6 t6 MPSoC CoreManager CP Processor 3 Processor 0 Processor 1 Processor 2 Heterogeneous MPSoC with Hardware Supported Dynamic Task Scheduling for SDR

Heterogeneous MPSoC: ‘Tomahawk’ 100 mm² @ 130 nm UMC; 40 GOPS, 1.5 W @ 175 MHz Scratchpad Memory 3.8 mm², ~85 mW Vector Fixed Point DSP Core Manager 5.9 mm² ~280 mW 2.5 mm² ~30 mW 10 mm Control Processor 3.3 mm², ~27 mW Scalar Floating Point DSP LDPC Decoder Filter ASIP Peripherals 10 mm Heterogeneous MPSoC with Hardware Supported Dynamic Task Scheduling for SDR

Software Scaling Results • Scalability depends on: • Task-to-Scheduling time ratio • Inter-Task dependency • Baseband signal processing: • Task time ~102 – 104 cycles • SW scheduling: • ~1000 cycles/task • HW accelerated scheduling: ~60 cycles/task SpeedUp Number of Cores 0% or 50% probability of dependence between tasks, 4kB data transfers (in and out) Hardware task scheduling = power and performance efficient solution for MPSoC programming problem Heterogeneous MPSoC with Hardware Supported Dynamic Task Scheduling for SDR