Memory Management in Operating Systems

120 likes | 144 Views

Explore the intricacies of memory management in operating systems, covering topics of addressing, paging, segmentation, and access time calculations in this detailed problem set.

Memory Management in Operating Systems

E N D

Presentation Transcript

Suggested Exercise #5 Sarah Diesburg Operating Systems CS 3430

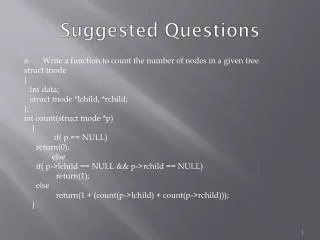

Problem 1 (a) • 32-bit addressing • Page size: 4 Kbytes (212 bytes) • Pure paging • 232 bytes / 212 bytes/entry= 220 entries • Each page table entry • 20-bit physical page number • 4 status bits • Page table size = 220 entries * 3 bytes/entry = 3 Mbytes

32 – 12 = 20 bits for 32-bit machines log2(4KB) = 12 bits for 4-KB pages Virtual page number Physical page number Offset Offset Page table size > Physical page number 220 entries Physical page number Physical page number Error Paging Diagram 4 status bits

Problem 1 (b) • Segmented-paging address translation • Page size: 4 Kbytes (212 bytes) • Offset: 12 bits • Three segments: code, data, stack • Virtual segment number: log23 = 2 bits • Virtual page number • 32 – 12 – 2 = 18 bits

32 - 2 - 12 = 18 bits 32 bits for 4-GB Page table base Page table bound 22 entries Page table base Page table bound Page table base Page table bound 12 bits for 4-KB pages 20 bits Seg # Virt page # Offset num of entries defined by bound; up to 218 entries Phy page # log2(3 segments) = 2 bits Phy page # Phy page # Segmented Paging

32 – 2 – 12 = 18 bits 218 Seg # Virt page # Offset Page table size > Phy page # Phy page # Phy page # Error Segmented Paging Page table base + Phy page # Offset log2(4GB) = 32 bits

Problem 1 (b) • Each segment (code, data, stack) uses 16 Kbytes = 4 pages • 3 page tables: • Code-segment page table: 4 entries • Page table entry • 20 bits to address all physical page numbers • 4 status bits • 24 bits/entry * 4 entries = 96 bits • Same for data-segment page table and stack-segment page table • Total: 96 bits * 3 = 288 bits

Problem 1 (b) • 1 segment table: • 4 entries • 32 bits for the page table base • 18 bits for the page table number bound • 4 status bits • Total memory: 4 * (32 + 18 + 4) = 216 bits

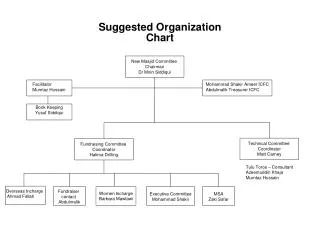

Problem 2 • Effective access time = P(hit)*cost(hit) + P(miss)*cost(miss) = P(L1 hit)*cost(L1 hit) + P(L1 miss)*cost(L1 miss) = 98%*(1 clock cycle) + 2%*cost(L1_miss)

Problem 2 • What is cost(L1_miss)? • cost(L1_miss) = P(L2_hit)*cost(L1_miss+L2_hit) + P(L2_miss)*cost(L1_miss+L2_miss+mem_hit)

Problem 2 L1 98% 1 cycle 2% 1 cycle hit L2 1% 2 cycles 99% 2 cycles memory hit 100% 6 cycles hit

Problem 2 • Effective access time = 98%*1 + 2%*99%(1 + 2) + 2%*1%(1 + 2 + 6) L1 98% 1 cycle 2% 1 cycle hit L2 1% 2 cycles 99% 2 cycles memory hit 100% 6 cycles hit