4.1 原理图方式设计初步

第4章 原理图输入设计方法. 4.1 原理图方式设计初步. 4.1.1 基本设计步骤. 步骤1:为本项工程设计建立文件夹. 注意: 文件夹名不能用中文,且不可带空格。. 为设计全加器 新建一个文 件夹作工作库. 文件夹名取为 My_prjct 注意,不可 用中文!. 使用原理图输入 方法设计,必须 选择打开原理图 编辑器. 步骤2:输入设计项目和存盘. 新建一个设 计文件. 图4-1 进入 MAX+plusII, 建立一个新的设计文件. 首先在这里用 鼠标右键产生 此窗,并选择 “ Enter Symbol” 输入一个元件.

4.1 原理图方式设计初步

E N D

Presentation Transcript

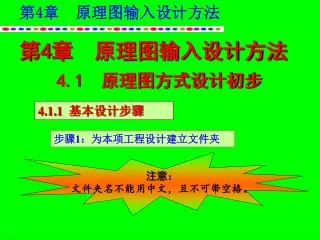

第4章 原理图输入设计方法 4.1 原理图方式设计初步 4.1.1 基本设计步骤 步骤1:为本项工程设计建立文件夹 注意: 文件夹名不能用中文,且不可带空格。

为设计全加器 新建一个文 件夹作工作库 文件夹名取为 My_prjct 注意,不可 用中文!

使用原理图输入 方法设计,必须 选择打开原理图 编辑器 步骤2:输入设计项目和存盘 新建一个设 计文件 图4-1 进入MAX+plusII,建立一个新的设计文件

首先在这里用 鼠标右键产生 此窗,并选择 “Enter Symbol” 输入一个元件 也可在这里输 入元件名,如 2输入与门 AND2,输 出引脚: OUTPUT 然后用鼠 标双击这 基本硬件库 这是基本硬件库 中的各种逻辑元件 图4-2 元件输入对话框

·Prim: Altera的图元(基本逻辑块)。 ·Mf:74系列逻辑等效宏库。 ·Mega-lpm:参数化模块库、 宏功能高级模块(如 busmux、 csfifo、 cadram、 parallel-add等)和IP功能模块(如UARTs、 FFT、 FIR、 PCI等)。 ·edif: edif接口库。

在图形设计文件中输入图元和宏功能符号的步骤如下:在图形设计文件中输入图元和宏功能符号的步骤如下: 1) 输入Altera 图元 10 选择工具按钮有效时, 在图形编辑器窗口的空白处单击鼠标左键以确定输入位置。 20 在Symbol菜单中选择Enter Symbol或单击鼠标右键并选择Enter Symbol, 或双击鼠标左键, 将出现一个Enter Symbol 对话框, 在Symbol Libraries框中双击选择“..\maxplus2\max2lib\prim”。 30 所有的Altera 图元以列表方式显示出来, 选择你想输入的图元, 然后双击或选择 OK按钮。 此时所选中的图元就出现在图形编辑器窗口中。 只要重复上述三步, 就可连续选取图元。

2) 输入74系列的符号 74 系列的符号的输入方法与图元的输入方法相似。 10 当Enter Symbol 对话框出现后, 在Symbol Libraries 对话框中双击选择 “.\maxplus2\max2lib\mf”路径。 20 在 Symbol Files 对话框中选择需要的 74 系列符号, 然后双击或选择 OK按钮, 所选中的74 系列符号就出现在图形编辑器窗口中, 如图4.2-2所示。 图中的74138就是所选中的74 系列符号。 如要连续选取74 系列器件, 则只要重复上述几步就可以了。

3) 输入 LPM 符号 LPM(Library Parameterized Megafunction)符号的输入方法与前两种符号的输入方法相似。 10 在Enter Symbol对话框出现后, 在Symbol Libraries框中双击选择 “.\maxplus2\max2lib\mega-lpm”路径。 20在 Symbol Files 框中选择需要的 lpm 符号, 然后点击 OK按钮, 或双击选择需要的 lpm 符号。 此时lpm 符号就出现在图形编辑器窗口中, 并出现输入参数对话框, 如图4.2-3 所示。 输入需要的参数后点击OK按钮。

30 在图形编辑器窗中双击lpm符号的参数框 (位于符号的右上角), 也出现lpm符号参数对话框, 可输入或改变参数。 在Port Status 框中选择 Unused , 可将不需要的信号去掉。 40 也可利用MegaWizard Plug In Manager 输入宏功能符号和LPM库函数。 如输入一个存储器的步骤如下: 在图形编辑器窗口空白处双击鼠标左键, 出现Enter Symbol对话框后点击MegaWizard PlugIn Manager按钮, 或在File菜单中选择MegaWizard Plug In Manager项, 然后选中Create a new custom megafunction variation, 再点击Next按钮。

在Available Megafunctions 列举中点击“+”按钮, 扩展storage文件夹, 然后选择 LPM-ROM, 在右边的对话框中输入你所希望的输出文件名和类型, 如rom和AHDL,如图4.2-4所示。 在其后的address input bus宽度输入8, q output bus宽度输入4, 输出符号名为rom, 其它为缺省值, 然后点击OK按钮。 在所希望的地方点击左键插入rom符号。 一个新名为rom的符号出现在图形编辑器窗中, 双击rom符号, 还可对具体参数进行编辑。 用户以后就可以直接调用该符号了。

输出引脚: OUTPUT 输入引脚: INPUT 图4-3 将所需元件全部调入原理图编辑窗 将它们连接 成半加器 连接好的原理图

连线 如果需要连接两个端口, 可将鼠标移到其中一个端口, 这时鼠标自动变为“+”形状, 然后可按以下步骤操作: (1) 一直按住鼠标的左键并将鼠标拖到第二个端口。 (2) 放开左键, 则一条连接线被画好了。 (3) 如果需要删除一根连接线, 单击这根连接线并按 Del 键即可, 如图4.2-5所示。

为引脚和节点命名 1) 放置输入引脚和输出引脚 放置输入引脚和输出引脚的方法与图元的输入方法相似, 即在图形编辑器窗口的空白处单击鼠标左键以确定输入位置, 然后在Symbol菜单中选择Enter Symbol或双击鼠标左键, 将出现一个Enter Symbol 对话框。 只要在Enter Symbol对话框中键入Input(Output), 然后选择 OK按钮, 符号INPUT(OUTPUT)就出现在图形编辑器窗口中。

如果要重复放置同一符号或器件, 用复制的方法, 可提高图形输入的效率。 一种是利用edit中的copy命令进行复制, 另外一种方法是将鼠标放在所要复制的符号或器件上, 按下Ctrl键和鼠标左键不放, 拖曳鼠标至所需要的位置, 这样就完成了符号或器件的复制。

2) 为引脚命名 在引脚上的PIN-NAME处双击鼠标左键, 然后输入指定的名字。 3) 为连线命名 点击鼠标左键选中需命名的线, 然后输入名字。 对 n 位宽的总线 A 命名时, 可以采用 A[n 1..0] 形式, 其中单个信号用 A0, A1, A2, …, An 形式 。

文件名取为: h_adder.gdf 首先点击这里 注意,要存在 自己建立的 文件夹中 图4-4 连接好原理图并存盘

步骤3:将设计项目设置成工程文件(PROJECT) 最后注意此路 径指向的改变 首先点击这里 然后选择此项, 将当前的原理图 设计文件设置成 工程 图4-5 将当前设计文件设置成工程文件

注意,此路径指 向当前的工程!

步骤4:选择目标器件并编译 首先选择这里 器件系列选择 窗,选择ACEX1K 系列 根据实验板上的 目标器件型号选 择,如选EP1K30 注意,首先消去 这里的勾,以便使所 有速度级别的器件都 能显示出来 图4-6 选择最后实现本项设计的目标器件

选择编译器 编译窗 图4-7 对工程文件进行编译、综合和适配等操作

消去Quartus适配操作 选择此项 消去这里的勾

首先选择此项, 为仿真测试新 建一个文件 步骤5:时序仿真和包装入库 选择波形 编辑器文件 (1) 建立波形文件。

从SNF文件中 输入设计文件 的信号节点 SNF文件中 的信号节点 点击“LIST” (2) 输入信号节点。 图4-8 从SNF文件中输入设计文件的信号节点

用此键选择左窗 中需要的信号 进入右窗 最后点击“OK” 图4-9 列出并选择需要观察的信号节点

消去这里的勾, 以便方便设置 输入电平 (3) 设置波形参量。 图4-9 列出并选择需要观察的信号节点 图4-10 在Options菜单中消去网格对齐Snap to Grid的选择(消去对勾)

(4) 设定仿真时间。 选择END TIME 调整仿真时间 区域。 选择60微秒 比较合适 图4-11 设定仿真时间

(6) 波形文件存盘。 (5) 加上输入信号。 用此键改 仿真区域坐标 到合适位置。 点击‘1’,使 拖黑的电平 为高电平 图4-12 为输入信号设定必要的测试电平或数据 图4-13 保存仿真波形文件

(7) 运行仿真器。 选择仿真器 运行仿真器 图4-14 运行仿真器

(8) 观察分析半加器仿真波形。 图4-15 半加器h_adder.gdf的仿真波形

选择时序 分析器 输入输出 时间延迟 图4-16 打开延时时序分析窗 (9) 为了精确测量半加器输入与输出波形间的延时量,可打开时序分析器.

(10) 包装元件入库。 选择菜单“File”→“Open”,在“Open”对话框中选择原理图编辑文件选项“Graphic Editor Files”,然后选择h_adder.gdf,重新打开半加器设计文件,然后选择如图4-5中“File”菜单的“Create Default Symbol”项,将当前文件变成了一个包装好的单一元件(Symbol),并被放置在工程路径指定的目录中以备后用。

选择引脚 锁定选项 引脚窗 步骤6:引脚锁定

此处输入 信号名 此处输入 引脚名 注意引脚属性 错误引脚名将 无正确属性! 按键 “ADD” 即可

再编译一次, 将引脚信息 进去

选择编程器, 准备将设计 好的半加器 文件下载到目 器件中去 编程窗

在编程窗打开 的情况下选择 下载方式设置 步骤7:编程下载 (1) 下载方式设定。 选择此项下 载方式 图4-18 设置编程下载方式

步骤7:编程下载 (1) 下载方式设定。 下载(配置) 成功! (2) 下载。 图4-19 向EF1K30下载配置文件 图4-18 设置编程下载方式

(1) 仿照前面的“步骤2”,打开一个新的原理图编辑窗口 步骤8:设计顶层文件 图4-20 在顶层编辑窗中调出已设计好的半加器元件

(2) 完成全加器原理图设计,并以文件名f_adder.gdf存在同一目录中。 图4-21 在顶层编辑窗中设计好全加器 (3) 将当前文件设置成Project,并选择目标器件为EPF10K10LC84-4。 (4) 编译此顶层文件f_adder.gdf,然后建立波形仿真文件。

(5) 对应f_adder.gdf的波形仿真文件,参考图中输入信号cin、bin和ain输入信号电平的设置,启动仿真器Simulator,观察输出波形的情况。 图4-22 1位全加器的时序仿真波形 (6) 锁定引脚、编译并编程下载,硬件实测此全加器的逻辑功能。

4.1.2 设计流程归纳 图4-23 MAX+plusII一般设计流程

4.2 较复杂电路的原理图设计 4.2.1 设计有时钟使能的两位十进制计数器 (1) 设计电路原理图 图4-24 用74390设计一个有时钟使能的两位十进制计数器

(2) 计数器电路实现 图4-25 调出元件74390 图4-26 从Help中了解74390的详细功能

(3) 波形仿真 图4-27 两位十进制计数器工作波形

4.2.2 频率计主结构电路设计 图4-28 两位十进制频率计顶层设计原理图文件