The Deep Fried Game Station

290 likes | 427 Views

This document outlines the design and functionality of an arcade-style video game station capable of running Tetris, featuring a MC68000 processor and dual-port video RAM. It provides audio-video output via composite video and accepts user input through a button controller. The system comprises dedicated video and audio units, supporting a nostalgic gaming experience. The paper details milestones, parts lists, and a schedule for development, emphasizing the integration of hardware and software components, culminating in a user-friendly gaming interface.

The Deep Fried Game Station

E N D

Presentation Transcript

The Deep Fried Game Station Team Monte Cristo Joseph Carrafa Sharon Clark Scott Hassett Alex Mason

Overview Functionality Block Diagram Hardware CPU and Memory Video Circuit Sound Circuit HID Software Schedule Full Schedule Milestones Division of Labor Parts Parts Lists Costs Conclusion Table of Contents

Overview • System Functionality • Prototype an arcade style game station capable of running a video game • Provide audio-video output (video via Composite Video) • Accept user input via button presses • Program Tetris as the demonstrable video game for the game station

Features • Video Game Station • Capable of running any comparably sized video game • Separate Video & Audio Units • Button Controller • Rotate, Move Left, Move Right • TV Connectable • Outputs the Game on any TV • Tetris • The Childhood favorite is back to stay

MC68000 MC68000 Block Diagram Audio EPROM RAM Data Bus Dual Port VRAM Controller Serial Port FPGA Composite Video

CPU and Memory • MC68000 • Large Address Space • RAM • 4Mb SRAM • 1kb VRAM CY7C144

Video Features • 1 Kilobyte of Dual-Port Video RAM • 105 pixels per row at 0.5 microseconds per pixel • 78 pixels per column at 6 rows per pixel • Total of 8190 pixels per screen, at 8 pixels per byte • CPU writes to VRAM, FPGA reads from VRAM at same time • FPGA Outputs NTSC Compliant Signal • Interlacing at 60Hz • Blanking Syncing and Interlace Syncing • Analog FPGA output eliminates need for DAC

Video Circuit I/O • FPGA only reads from VRAM, never writes • Reads data at the same time that MC68000 writes data

FGPA Logic Circuit - Bit Input to Row Registers • Sequentially steps through VRAM automatically • Shifts pixels into Row REGISTERS • Loads 105 pixels at a time (one row)

FGPA Logic Circuit - Row Registers to Video Output • Series of Counters Control Syncing • Onboard DACs sum voltage to produce NTSC signal

Sound Features • Background Music • ~10 seconds • Looping • Triggered to start/stop by processor • Uses a single ISD1212 chip • Row Win Music • ~3-5 seconds • Processor sends address and signals chip to play • End of Game Music • ~5-7 seconds • Processor sends address and signals chip to play • Row Win music and End of Game music share an ISD1212 chip

ISD1212 Pinouts • REC records when input is low • PLAYE, PLAYL play when input is low • When A7, A6 are low, A0-A5 act as address pins • When A7, A6 are high, A0-A5 act as Operational Modes • Looping Operation Mode occurs when A3 is high

Circuit Diagram for Background Music PLAYE PLAYL • A7,A6,A3 set to high to enable looping • Pulsing PLAYE starts playback • Pulsing PLAYL ends playback • Taking PLAYE high during a playback cycle will not terminate the current cycle

Circuit Diagram for Row Win Music and End of Game Music • A7, A6 set to low to enable addressing • A0-A5 determine address of music clips • Processor enables Chip Select and Sends Address of sound to play • Processor enables Chip Select Signal and Play Signal to play sound at that address

Design of Button Circuit Design of Button Circuit

Design of Button Circuit Multiple Buttons Buttons can be cascaded in this manner

Controller Mock-up Three button layout *NOTE* Sharp Edges may induce hand cramps!

Software • Implement Tetris • Discrete Nature • Scoring • More Button Functionality • Inputs • A button – Rotate Current Block • B button – Move Left • C button – Move Right

Milestone 1 Complete development of individual modules Get board to interface with video display device Milestone 2 Integrate modules Run test executable to demonstrate working hardware Intermediate Deadlines

Expo Implement Tetris as final demonstration of functional game station. User can interface with device using HID to change the screen output Basic scoring and game rules implemented Background, Row Win and End Game Music Final Goals

Division of Labor • Joe Microprocessor Software • Alex Video Module • Sharon Sound Module • Scott HID and Interface

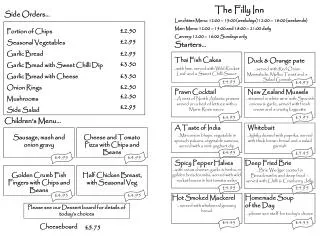

Parts List with Costs Description Price Quantity Total • Main Board: Breadboard Aesthetically Challenged Free 1 $0.00 Processor MC68000 Free 1 $0.00 EPROM Free 2 $0.00 FPGA Free 1 $0.00 Memory Dual Port CY7C144 Free 1 $0.00 Misc. Parts NANDS/Resistors/Capacitors/Etc Free $0.00 • Video Module: Composite Video Cable $10 1 $10.00 TV Free 1 $0.00 • Sound Module: Sound Chip ISD1212 $4.50 2 $9.00 Microphone P9931 $1.26 1 $1.26 • Controller: Analog Buttons $0.58 3 $1.74 Casing Materials $15.00 $15.00 Total: $37.00

Conclusion • Video Game Station • MC68000 Processor • Video Module • Sound Module • Controller • Runs Tetris as Demonstrable Game