5 、 设计下载 :

QuartusⅡ 设计流程. 5 、 设计下载 :

5 、 设计下载 :

E N D

Presentation Transcript

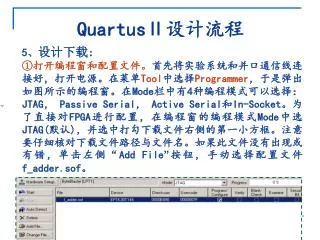

QuartusⅡ设计流程 5、设计下载: ①打开编程窗和配置文件。首先将实验系统和并口通信线连接好,打开电源。在菜单Tool中选择Programmer,于是弹出如图所示的编程窗。在Mode栏中有4种编程模式可以选择:JTAG, Passive Serial, Active Serial和In-Socket。为了直接对FPGA进行配置,在编程窗的编程模式Mode中选JTAG(默认),并选中打勾下载文件右侧的第一小方框。注意要仔细核对下载文件路径与文件名。如果此文件没有出现或有错,单击左侧“Add File”按钮,手动选择配置文件f_adder.sof。

QuartusⅡ设计流程 5、设计下载: ②设置编程器。若是初次安装的QuartusⅡ,在编程前必须进行编程器选择操作。这里准备选择ByteBlaster MV[LPT1]。单击Hardware Setup按钮可设置下载接口方式,在弹出的Hardware Setup对话框中,选择Hardware settings页,再双击此页中的选项BytcBlaster之后,单击Close按钮,关闭对话框即可。这时应该在编程窗右上显示出编程方式:ytcBlaster [LPT 1]。如果打开下所示的窗口内“Currently selected”右侧显示No Hardware,则必须加入下载方式。即点击Add Hardware钮,在弹出的窗中点击OK,再在窗口中双击BytcBlaster,使“Currently selected”右侧显示BytcBlaster [LPT1]。

QuartusⅡ设计流程 5、设计下载: ③下载:单击下载标符Start按钮,即进入对目标器件FPGA的配置下载操作。当Progress显示出100%,以及在底部的处理栏中出现“Configuration Succeeded”时,表示编程成功。注意,如果必要,可再次单击Start按钮,直至编程成功。 ④硬件测试:软件下载成功后,测试已完成电路是否符合设计要求。

模60的计数器设计与实现 建立图形文件:打开Quartus Ⅱ 5.0编辑器,选择File/New命令,在Device Design File选项卡下选择Block Digram /Schematic File,单击OK按钮。 QuartusⅡ设计应用举例 模为60的计数器原理图

下载模式 • ByteBlaster并口下载电缆提供两种下载模式: • (1)被动串行模式(PS模式)——用于配置FLEX 10K、FLEX 8000和FLEX 6000器件; • (2)JTAG模式——具有工业标准的JTAG边界扫描测试电路(符合IEEE 1149.1:1990标准),用于配置FLEX 10K或对MAX 9000、MAX 7000S和MAX 7000A器件进行编程。

GW48-PK系列实验开发系统使用说明 • 1.闲置不用GW48系列EDA系统时,必须关闭电源,拔下电源插头; • 2.在实验中,当选中某种模式后,要按一下右侧的复位键,以使系统进入该结构模式工作; • 3.换目标芯片时要特别注意,不要插反或插错,也不要带电插拔,确信插对后才能开电源。其他接口都可带电插拔。请特别注意,尽可能不要随意插拔适配板及实验系统上的其他芯片;

GW48-PK系列实验开发系统使用说明 • 4.PC机的并行口工作模式设置在“EPP”模式; • 5.对于GW48-CK/PK系统,主板左侧上开关默认向下,关闭+/-12V电源;下开关默认向上,允许下载; • 6.跳线座“SPS”默认向下短路(PIO48),右侧开关默认拨向右(TO MCU); • 7.对于GW48-CK/PK系统,左下角拨码开关除第四档“DSB8使能”向下拨外,其余都默认向上;

GW48-PK系列实验开发系统使用说明 • 8.对于右下角的“时钟频率选择”区的“clock0”上的短路帽,平时不要插在50/100M高频处,以免高频辐射; • 9.若实验系统或开发板上的FPGA目标器件是低压器件,如EP20K系列,EP1K系列,MAX3000A系列等,当外部TTL电平信号输向此类FPGA的IO口或专用输入端时,必须串接100至200欧姆电阻。