Slow Control

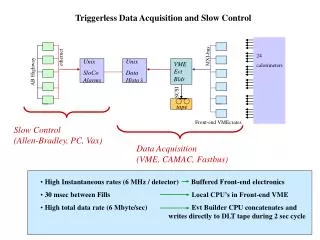

Slow Control. TPC Electronics Meeting, 13/01/05 Carmen Gonz ález Gutiérrez. Slow Control Architecture. RCU. Local Slow Control Interface. commands. error. Ethernet. central DCS. BC. interrupt. warnings. FEC. DCS board. Result Memory. Local Slow Control bus

Slow Control

E N D

Presentation Transcript

Slow Control TPC Electronics Meeting, 13/01/05 Carmen González Gutiérrez

Slow Control Architecture RCU Local Slow Control Interface commands error Ethernet central DCS BC interrupt warnings FEC DCS board Result Memory Local Slow Control bus ~ I2C protocol: 2 unidirectional serial data lines 1 serial clock line

Board Controller • Enable the clocks and the power supply of the board • Control the power state, voltages, currents and temperature of the FECs • 4-channel ADC with a temperature sensor and I2C Interface • compare the result with a configurable thresholds • Register the errors of the board • Alert the RCU (INTERRUPT) in case of an abnormal situation in the board • Control the enable of the transceivers in INPUT or OUTPUT • Launch the ALTRO TEST MODE • isolate the card from the Readout bus • set the ALTRO in Test Mode • store the data with a number of words and under-sampling ratio configurable • Scan the EVENT LENGTH of the ALTRO for the Readout optimization • BC is master of the ALTRO • set 128-bit EVL register (1 bit per channel) • send the EVL register value in 4 - 40 bit words to the ALTRO bus Interface • Counters • L1 and L2 counters • Sampling clock counter • Data Strobe counter

Slow Control Architecture RCU Local Slow Control Interface commands Ethernet central DCS BC interrupt warnings FEC DCS board Result Memory Local Slow Control bus ~ I2C protocol: 2 unidirectional serial data lines 1 clock line

Instruction Sequence • start condition (1 clock cycle) • 1 byte (9 clock cycles) • bit [0] : read / write • bit [1..4] : FEC address • bit [5] = x • bit [6] : bcast • bit [7] = x • WAIT FOR THE ACKNOWLEDGE FROM THE ADDRESSED CARD • 1 byte (9 clock cycles) • bit [0..4] : register address to access in the BC • bit [5..7] : x • WAIT FOR THE ACKNOWLEDGE FROM THE ADDRESSED CARD • 2 bytes (18 clock cycles) • bit [0 ..7]: DATA • WAIT FOR THE ACKNOWLEDGE FROM THE ADDRESSED CARD AFTER EACH BYTE • stop condition (1 clock cycle) Every transaction requires the following sequence (6 words)

Local Slow Control Architecture Local Slow Control Module Instruction Sequence (6 words) address Sequencer Instruction Sequence Builder data command addresser we sda_in • Send information about: • write or read cycle • FEC address, broadcast • register address BC scl MASTER sda_out RESULT Memory

Normal mode • The DCS sends commands continuously to the SCM for monitoring the FEC • Temperature • Digital and Analog Voltages • Digital and Analog Currents • Control of triggers • send in broadcast the command to latch the counters in the BCs • compare the value of all the counters • The DCS reads the values and controls the margins of each parameter RCU Local Slow Control Interface DCS board commands BC Master CENTRAL DCS FEC Result Memory Local Slow Control bus

Board Controller, ERRORS • Errors asserted by the BC • Temperature over threshold • Analog or Digital voltages under threshold • Analog or Digital currents over threshold • Power supply error (related to the ALTRO or the PASA) • Missing sampling clk • Protocol errors (from the ALTRO bus or the Slow Control) • ALTRO error • Error asserted by the voltage regulators that supply: • GTL transceivers • FPGA • Clock distribution • EPROM • mADC THESE ERRORS ASSERT THE INTERRUPT OR THE ERROR LINE power regulator ALTRO ps_error power regulator PASA ps_error power regulator GTL, FPGA, clock interrupt power regulator EPROM, mADC interrupt

INTERRUPT What the Slow Control Module does if the RCU receives an interrupt ? • The SCM starts polling the error register of each FEC (via the Local Slow Control bus) to identify the source (which FEC and the error) • Different procedures will start depending of the error: RCU Local Slow Control Interface commands interrupt BC Master warnings DCS board FEC Result Memory Local Slow Control bus

INTERRUPT • “Hard” errors • Analog or Digital currents over thresholds • Power supply errors • ALTRO or PASA power supply errors • Error in the power regulator that supply GTL transceivers, FPGA, clock distribution, EPROM and monitor ADC • Switch off immediately the card and inform the DCS • “Soft” errors • Temperature over threshold • Analog or Digital voltages under threshold • Missing sampling clk • Remove the card from the READOUT LIST, mask that error in the BC and inform the DCS

In case of INTERRUPT: Local Slow Control Module Instruction Sequence address Sequencer Instruction Sequence Builder data command addresser we sda_in • Send information about: • write or read cycle • FEC address, broadcast • register address scl MASTER BC sda_out Interrupt Interrupt driver warning to the DCS Readout List • Depending of the Interrupt: • Switch off the card, inform the DCS • Remove the card from the Readout List, mask the error, inform the DCS

Status of the work • Completed tested • All the functions of the BC: • Write/Read the configuration parameters • Read all the parameters of the board (temp, voltages, currents, counters …) • ALTRO Test mode • ALTRO Readout optimization • Error flags • Interrupt assertion • The communication between the SCM and the BC • Performance: • The Local Slow Control network runs at a clock frequency of 5 MHz. • The protocol requires the transmission of a large number of control words. A single 16-data bit transaction, e.g., requires 8 µs. • When an interrupt occurs, the RCU starts polling the error/status register of all FECs of one branch. This action could require up to 100 µs in the case of a readout partition with 13 FEC/branch.

Status of the work • Work to be done: • Complete definition and implementation of the response to an Interrupt in the SCM • Definition of all the routines in the DCS • In normal mode (monitor the status of the cards) • Safety procedures in case of problems