Understanding Instruction Handling in PIC CPU: Analyzing Fetch and Execute Cycle

This document delves into the intricacies of instruction handling within the PIC CPU architecture. It covers the processes of fetching instruction sequences from memory, managing the instruction register, and the role of the program counter. Additionally, it discusses interrupt handling, including non-maskable interrupts (NMI) and their corresponding vectors. Through a detailed examination of microprograms and the execution cycle, the content provides a comprehensive understanding of how the CPU executes instructions efficiently and responds to interrupts, ensuring reliable operation of embedded systems.

Understanding Instruction Handling in PIC CPU: Analyzing Fetch and Execute Cycle

E N D

Presentation Transcript

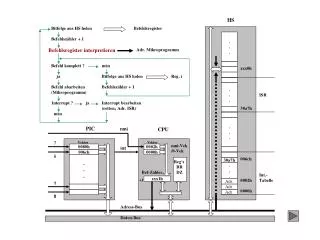

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR 1nterrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 xxx1h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR 1nterrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 xxx1h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 xxx1h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR Interrupt ? ja Interrupt bearbeiten (retten;Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 006ch 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 30a7h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 30a7h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 30a8h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 30a8h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . 3xxxh ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 3xxxh 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i 3endh reti Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . 3xxxh ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 3end+1h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i 3endh reti Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . 3xxxh ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 xxx1h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus

HS Bitfolge aus HS holen Befehlsregister . . . Befehlszähler + 1 Befehlsregister interpretieren Adr. Mikroprogramm Befehl komplett ? nein xxx0h ja Bitfolge aus HS holen Reg. i 3endh reti Befehl abarbeiten (Mikroprogramm) Befehlszähler + 1 . . . 3xxxh ISR Interrupt ? ja Interrupt bearbeiten (retten; Adr. ISR) 30a7h nein . . . PIC CPU nmi 7 Vektor Vektor nmi-Vek 0080h int 0002h /0-Vek xxx1h 006ch 0000h 6 . . . 006ch Reg‘s 30a7h BR . . . Bef-Zähler DZ Int.- Tabelle +1 xxx1h 0002h 1 Adr. Adr. 0000h Adr. 0 Adress-Bus Daten-Bus