第4章 同步时序逻辑电路-1

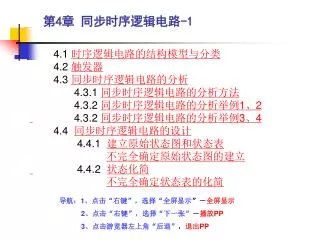

第4章 同步时序逻辑电路-1. 4.1 时序逻辑电路的结构模型 与分类 4.2 触发器 4.3 同步时序逻辑电路的分析 4.3.1 同步时序逻辑电路的分析方法 4.3.2 同步时序逻辑电路的分析举例 1、2 4.3.2 同步时序逻辑电路的分析举例 3、4 4.4 同步时序逻辑电路的设计 4.4.1 建立原始状态图和状态表 不完全确 定 原始状态图 的建立 4.4.2 状态化简

第4章 同步时序逻辑电路-1

E N D

Presentation Transcript

第4章 同步时序逻辑电路-1 4.1 时序逻辑电路的结构模型与分类 4.2 触发器 4.3 同步时序逻辑电路的分析 4.3.1同步时序逻辑电路的分析方法 4.3.2 同步时序逻辑电路的分析举例1、2 4.3.2 同步时序逻辑电路的分析举例3、4 4.4 同步时序逻辑电路的设计 4.4.1 建立原始状态图和状态表 不完全确定原始状态图的建立 4.4.2 状态化简 不完全确定状态表的化简 导航:1、点击“右键”,选择“全屏显示”-全屏显示 2、点击“右键”,选择“下一张”-播放PP 3、点击游览器左上角“后退”,退出PP

第4章 同步时序逻辑电路 概述 数字逻辑电路可以分为两大类: 1、组合逻辑电路和时序逻辑电路。组合逻辑电路是:电路在任何时刻所产生的输出,仅取决于该时刻电路的输入。 2、时序逻辑电路是:电路在任何时刻电路的状态和输出不但取决于该时刻电路的输入,还与电路过去的状态有关。 时序逻辑电路可以分为: 1、同步时序逻辑电路; 2、异步时序逻辑电路; 本章首先介绍时序逻辑电路的基本概念,然后介绍同步时序逻辑电路的分析和设计方法。

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 4.1.1结构模型时序逻辑电路的结构模型如图4-1所示。 时序逻辑电路实例: 外部输入 时钟输入 外部输出 存储电路的输出 内部输入

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 时序逻辑电路的工作过程:理解时序逻辑电路外部输入、外部输入、时序逻辑电路的状态、内部输入的概念 0 0 0 1 1 0 0 0 1 1 0 0 0 0 1 1 Z 次态 次态 现态 现态

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 4.1.2时序逻辑电路的分类 时序逻辑电路分为: 1、同步时序逻辑电路; 2、异步时序逻辑电路; 最重要的不同特点: 1、在同步时序逻辑电路中,存储电路中所有触发器的时钟输入端都接于同一个时钟脉冲。因而,所有触发器的翻转都与时钟脉冲信号同步。 2、在异步时序逻辑电路中,没有统一的时钟脉冲。因此在异步时序逻辑电路中,触发器的时钟输入端如果有时钟,触发器就翻转。如果触发器的时钟输入端如果没有时钟,触发器就不翻转。

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 4.1.4 同步时序逻辑电路的描述方法 如前所述,同步时序逻辑电路的输出不仅取决于电路在该时刻的输入,还与电路的现态有关。因而,用输入和输出取值关系的真值表来描述它的逻辑功能是不够。 为了表达同步时序逻辑电路的输入、输出、现态和次态之间转移的动态关系,需要使用有向图来表示同步时序逻辑电路的动态关系。这种有向图称为状态转移图,简称状态图。状态图采用图形的方式表达状态转移,因而具有直观性。另外还使用表格来表示同步时序逻辑电路的动态关系,这种表格称为状态转移表,简称状态表。此外还用时间图、状态响应序列等方法表示同步时序电路的状态转移。 下面介绍同步时序逻辑电路的描述方法。

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 2.状态表 反映同步时序逻辑电路的外部输入x、现态yi、输出Z和次态y(n+1)之间对应取值关系的表格称为状态表。由于有两种类型的同步时序逻辑电路,因此状态表也有两种形式:一种称为Mealy型同步时序逻辑电路的状态表;另一种称为Moore型同步时序逻辑电路的状态表。 1)Mealy型同步时序逻辑电路的状态表如表4-1 所示。

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 2)Moore型同步时序电路的状态表如表4-2所示。 由于Moore型同步时序逻辑电路外部输出仅与同步时序电路的现态有关。 Moore同步时序逻辑电路的某一个现态对应一个外部输出。因此,Moore型状态表将外部输出单独作为一列。 状态表表达的含义是: 同步时序电路处于某一现态,这一现态有一个外部输出。当有某一外部输入时,在时钟信号作用下,电路转移到某个次态。

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 3.状态图 另一种反映同步时序逻辑电路的外部输入x、现态yi、输出Z和次态y(n+1)之间对应取值关系的图形称为状态图。 在状态图中,用圆圈表示一个状态。圆圈内用字母或数字表示某个状态的名字。圆圈之间用带箭头有向线段连接起来,表示状态的转移方向。有向线段起始点连接的圆圈是现态,终止点箭头连接的圆圈是次态。

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 若有向线段起始点和终止点是同一个状态,说明在外部输入条件下,次态与现态相同。

第4章 同步时序逻辑电路 4.1 时序逻辑电路的结构模型与分类 4.时间图 时间图也称为时序逻辑电路的波形图 波形图使用电路的波形描述同步时序逻辑电路的外部输入x、现态yi、输出Z和次态y(n+1)之间的对应取值关系。 上面介绍的描述同步时序电路逻辑功能的方法可以互相转换。在介绍同步时序逻辑电路的分析和设计方法时,将具体讲述以上描述方法的应用。

第4章 同步时序逻辑电路 4.2.触发器 4.2.触发器 在同步时序逻辑电路中,常常采用触发器组成存储电路。触发器是具有保存“0”和“1”两种稳定状态的电路。在任一时刻,触发器只处于“0”和“1”其中的一种稳定状态。当触发器处于某一个稳定状态时,它能长期保持该稳定状态。只有在时钟信号到来时,它才翻转到另一个稳定状态,直到下一个时钟信号到来,再翻转到另一个状态。 触发器是存储一位二进制数的理想器件,被广泛用于同步时序逻辑电路中。目前广泛使用的有4种触发器: 1)R-S触发器,2)J-K触发器,3)D触发器,4)T触发器。

第4章 同步时序逻辑电路 4.2.触发器 4.2.1 R-S触发器 1.基本R-S触发器 基本R-S触发器是直接“复位-置位”触发器,也称为锁存器。它是构成各种触发器的基本组成部分。 基本R-S触发器可以由两个“或非”门交叉耦合组成,也可以由两个“与非”门交叉耦合组成,如图4-5和图4-6所示。

第4章 同步时序逻辑电路 4.2.触发器 若输入端R = 0,S = 0,触发器保持原来的状态不变。 若输入端R = 0,S = 1,使触发器置为“1”状态。 若输入端R = 1,S = 0,使触发器置为”0”状态。 不允许出现输入端R = 1、S = 1。在这种情况下,基本R-S触发器处于哪种状态不确定。由“或非”门组成的基本R-S触发器,输入与输出之间的逻辑关系如表4-3所示。

第4章 同步时序逻辑电路 4.2.触发器 2.时钟控制R-S触发器 基本R-S触发器的状态仅仅是由R、S输入端的输入引起的。在实际应用中,往往要求触发器的翻转的状态按一定时间节拍进行。也就是,触发器只能在时钟信号来到时候,R-S触发器才发生状态转换。在没有时钟信号到来时,无论R、S输入端怎么变化,触发器的状态保持不变。

第4章 同步时序逻辑电路 4.2.触发器 时钟控制R-S触发器解决了触发器状态变化的定时问题。但是,由于时钟信号具有一定宽度,在时钟信号有效期间,如果输入信号发生变化,触发器状态会跟着发生变化,从而在一次时钟信号有效期间,可能引起触发器多次状态翻转,这种现象称为空翻。空翻将造成触发器状态不确定。 解决空翻问题的根本途径是改进R-S触发器的电路结构。改进的时钟控制R-S触发器的逻辑电路如图4-10所示,称为主从R-S触发器。

第4章 同步时序逻辑电路 4.2.触发器 4.2.2 D触发器 时钟控制R-S触发器在时钟信号作用期间,当R和S的输入端同时为“1”时,触发器会出现状态不确定现象。为了解决这个问题,对时钟控制R-S触发器的控制电路作相应修改。如果使R和S输入端成为互补状态,这样就构成了单输入端的触发器,称为D触发器。D触发器的逻辑电路图和逻辑符号如图4-11所示。

第4章 同步时序逻辑电路 4.2.触发器 表4-6 D触发器功能表 表4-78的状态表,使用状态图描述 表4-78 D触发器状态表 D触发器的次态卡诺图 D触发器的状态方程为 Qn+1 = D

第4章 同步时序逻辑电路 4.2.触发器 维持阻塞D触发器,逻辑电路图和逻辑符号如图4-14所示。

第4章 同步时序逻辑电路 4.2.触发器 4.2.3 J-K触发器 在时钟控制R-S触发器中,为了消除时钟控制R-S触发器输入信号的约束条件,又使触发器有两个输入端,在时钟控制R-S触发器中增加两条交叉反馈线,并将输入端S改名为J,R改名为K,称为J-K触发器,逻辑电路图和逻辑符号如图4-15所示。

第4章 同步时序逻辑电路 4.2.触发器 4.2.4 T触发器 如果把J-K触发器的两个输入端J和K连接起来,用符号T表示输入端,这样就构成了T触发器。T触发器的逻辑电路图和逻辑符号如图4-19所示。

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 4.3.1同步时序逻辑电路的分析方法 同步时序逻辑电路分析: 根据给定的同步时序逻辑电路图,找出同步时序逻辑电路的在外部输入X(0或1)时候,现态yn与次态yn+1之间转移的规律,以及在状态转移的时候,他的外部输出Z。得到同步时序逻辑电路的逻辑功能。 同步时序电路的分析步骤如下: 第1步,根据给定的同步时序逻辑电路,列出输出函数表达式和激励函数表达式。 第2步,建立状态转移真值表。 第3步,做出同步时序逻辑电路状态表、状态图。 第4步,用文字说明同步时序逻辑电路的逻辑功能。 根据需要使用时间图描述电路的工作特性。 下面讲解同步时序逻辑电路的分析方法。

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 4.3.2 同步时序逻辑电路的分析举例 例 4-1 分析图4-22所示的同步时序逻辑电路。Moore型电路 重点:分析方法,可逆计数器 外部输入 外部输出 激励函数 解:第1步,列出激励函数和输出函数表达式 J2 = K2 = x⊕y1J1 = K1 = 1 Z=y1y2

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 电路的输入 电路的输出 第2步,建立状态转移真值表 输出 Z 0 0 J-K触发 器 的功能表 1 0 1 0 0 0 所有的现态 J2=K2=X⊕y1 所有的次态

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 第3步,做出状态表和状态图 Z 0 0 1 0 1 0 0 0 Z 根据状态转移真值表中 现态-次态填入 0 0 0 1

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 状态表: 状态图: 外部输入 Z 0 0 0 1

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 第4步,电路逻辑功能说明 该同步时序逻辑电路是一个可逆计数器: 1)当电路外部输入x = 0时,同步时序逻辑电路进行加1数;当加到11时,外部输出为1; 2)当电路外部输入x =1时,同步时序逻辑电路进行减1计;当减到11时,外部输出为1;

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 同步时序逻辑电路的状态响应序列。所谓状态响应序列是指在假定存在一个外部输入x序列时,同步时序逻辑电路现态与次态之间转移的情况。 设可逆计数器的初始状态y2 y1为00,设外部输入x的序列为:11110000,它的状态响应序列如下: Z 1 0 0 0 0 0 1 0

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 时间图:采用波形表达时序电路状态转移的逻辑特性 根据状态表或者状态图画出 时钟输入: 假定外部输入: 0 1 1 0 0 0 0 1 1 时序电路的状态转移;(约定:触发器下降沿翻转) 0 1 0 1 0 1 0 0 1 1 0 0 0 0 0 1 0 外部输出: 0 z

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 例4-2 分析图4-25所示的同步时序逻辑电路。 重点:序列检测器同步时序逻辑电路 解:第1步,列出激励函数和输出函数表达式

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 第2步,建立状态转移真值表 Z 0 0 0 0 0 0 1 0

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 第3步,做出状态表和状态图

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 状态表: 状态图: y2 y1 z 第4步,电路功能:该同步时序逻辑电路是一个“101”序列检测器。 cp 0 0 1 0 0 1 0 1 0 0 1 x

第4章 同步时序逻辑电路 4.3 同步时序逻辑电路的分析 第4步,设电路的初始状态y2 y1为0 0,外部输入 x的序列为01011101,电路的状态响应序列如下: