Chapter 1 Interconnect Extraction

Chapter 1 Interconnect Extraction. Prof. Lei He Electrical Engineering Department University of California, Los Angeles URL: eda.ee.ucla.edu Email: lhe@ee.ucla.edu. Outline. Capacitance Extraction Introduction Table based method Formula based method Inductance Extraction Introduction

Chapter 1 Interconnect Extraction

E N D

Presentation Transcript

Chapter 1Interconnect Extraction Prof. Lei He Electrical Engineering Department University of California, Los Angeles URL: eda.ee.ucla.edu Email: lhe@ee.ucla.edu

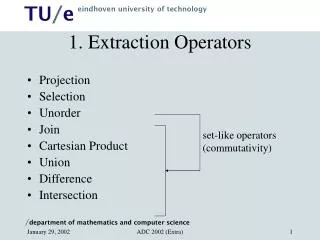

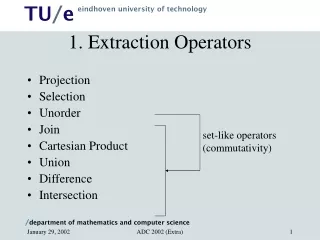

Outline • Capacitance Extraction • Introduction • Table based method • Formula based method • Inductance Extraction • Introduction • Table based method • Formula based method • RLC circuit model generation • Reading assignment • Finite element method (FEM) based Extraction • Overview of FEM • FEM based Extraction Flow • Reading assignment • Homework

++ ++ - - - - Capacitance - Introduction • What’s Capacitance? • Simplest model: parallel-plate capacitor • It has two parallel plates and homogeneous dielectric between them • The capacitance is • permittivity of dielectric • A area of plate • d distance between plates • The capacitance is the capacity to store charge • charge at each plate is • one is positive, the other is negative +Q -Q

c12 m2 m1 c23 c13 m3 Capacitance - Introduction • For multiple conductors of any shapes and materials, and in any dielectric, there is a capacitance between any two conductors (coupling capacitance). • Mutual capacitance between m1 and m2 is C12 = q1/v2 • q1 is the charge of m1 • v1 =0 and v3 = 0

c12 m2 c11 -c12 -c13 m1 c23 -c21 c22 -c23 C = -c31 -c32 c33 c13 m3 Capacitance - Introduction • How to represent Capacitance? • Capacitance is often represented by a symmetric matrix • is the self-capacitance for a conductor • e.g., c11 =c12+c13 • The charge is given by • e.g.,

Cx Cx Cx Capacitance - Introduction • How to calculate Capacitance? • Self-capacitance is sum of total coupling/mutual cap, i.e. • To the first order, capacitance exists only between adjacent wires or crossing wires, and can be pre-computed for a set of (localized) interconnect structures • Table based Cap. Extraction • Formula based Cap. Extraction

Capacitance – table/library based method • Table based Cap. Extraction (2.5D method) has two steps: • Table (Capacitance coefficients) generation • One-time use of 3-D method • Capacitance computation • Table lookup with linear interpolation and extrapolation • Reference: • [He-et al, DAC’97]

layer i Table generation • 1. Lateral, Area and Fringe Capacitances • Functions of (w,s) • Pre-computed for per-side per unit-length w s s

s sc layer i wc sc w Table generation (cont.) • 2. Crossing Capacitances • Function of (w,s,wc,sc)

Table generation (cont.) • 2. Crossing Capacitances s s sc wc wc sc sc w w Ci,i Per-corner Cover(w,s,wc,sc) = 4

victim Compute the lumped cap for victim Illustration of Capacitance Computation

S1 L1 w Per-side lateral capacitance = CL(w,s1) * L1 Per-side area capacitance = CA(w,s1) * L1 Per-side fringe capacitance = CF(w,s1) * L1 • Add in Per-Side Area, Fringe and Lateral Capacitances victim

Add in Per-Side Area, Fringe and Lateral Capacitances victim

w One-corner crossover correction = Cover(w,S1,wc,sc) • Add in Crossing Capacitances Corner-by-Corner victim S1 wc sc

w One-corner crossover correction = Cover(w,S1,wc,) • Add in Crossing Capacitances Corner-by-Corner victim S1 wc

w One-corner crossover correction = Cover(w,,wc,) • Add in Crossing Capacitances Corner-by-Corner victim S1 wc

w One-corner crossover correction = Cover(w,,wc,sc) • Add in Crossing Capacitances Corner-by-Corner victim wc sc

Summary of Capacitance Computation • Find nearest neighbors on the same layer. • Add in per-side lateral, area and fringe capacitance w.r.t. each neighbor. • Find all crossovers and crossunders. • Add in crossing capacitances corner-by-corner w.r.t. each crossover and crossunder. Sum of capacitance components in above steps is the lumped capacitance of the victim.

Capacitance – formula based method • Extract the Capacitance with analytical Formulae • Formula based on Horizontal and Vertical Parameters • Single Line • Parallel Lines • References: • [Sakurai-Tamaru,ED’83][Wu-Wong-et al, ISCAS’96]

Capacitance – formula based method • Single Line Example: • Unit-length capacitance: • Error less than 6% when [Sakurai-Tamaru, ED’83] w t Ff Ff h Fp

Capacitance – formula based method • Single Line of Length L • Line of length L [Sakurai-Tamaru, ED’83] w t h

Capacitance – formula based method • Two Parallel Lines on Same Layer • Unit-length capacitance: • Error less than 10% when [Sakurai-Tamaru, ED’83] s w w t h

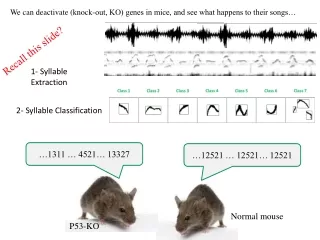

Capacitance – formula based method • Three Parallel Lines on Same Layer • Unit-length capacitance: • Recall [Wu-Wong-et al, ISCAS96] s s w w w t h [Sakurai-Tamaru, ED’83]

Capacitance – formula based method • Three Parallel Lines within Two Grounds • Two Grounds: where • One Ground: [Wu-Wong-et al, ISCAS96] s s w w w h1 t h1

Reading Assignment • [1] J. Cong, L. He, A. B. Kahng, D. Noice, N. Shirali and S. H.-C. Yen, "Analysis and Justification of a Simple, Practical 2 1/2-D Capacitance Extraction Methodology", ACM/IEEE Design Automation Conference, June 1997, pp.627-632 • [2]T.Sakurai, K.Tamaru, "Simple Formulas for Two- and Three-Dimensional Capacitances," IEEE Trans. Electron Devices ED-30 pp. 183-185 (Feb. 1983)

Outline Capacitance Extraction Introduction Table based method Formula based method Reading assignment Inductance Extraction Introduction Table based method Formula based method Reading assignment RLC circuit model generation Inductance screening Reading assignment Finite element method (FEM) based Extraction Overview of FEM FEM based Extraction Flow Reading assignment Homework

Inductance - Introduction • Is RC Model Sufficient? • As the clock frequency grows fast, the interconnect impedance is more than resistance Z = R + jωL • Inductance should be considered • When ωL becomes comparable to R as we move towards GHZ designs and 1/tr • Example: wide clock trees • Skews are different under RLC and RC models • Neighboring signals are disturbed due to large clock di/dt noise

Resistance vs Inductance Length = 2000, Width = 0.8 Thickness = 2.0, Space = 0.8 Ls and Lx for two parallel wires R and L for a single wire

Inductance - Introduction • Impact of Inductance 6000u 10u 5u 5u Gnd Clk Gnd RC model RLC model

Loop Inductance • Loop inductance is defined as • the induced magnetic flux in the loop • by the unit current in other loop • The average magnetic flux can be calculated by magnetic vector potential Aij Ij Loop i Loop j where, represents the magnetic flux in loop i due to a current Ij in loop j where, ai represents a cross section of loop i

Loop Inductance (cont.) • The magnetic vector potential A, defined as an integral form So, loop inductance is

2 1 3 5 4 Partial Inductance • Problems of loop inductance • The loops (called return paths) are hardly defined explicitly in VLSI • In most cases, the return paths are multiple • Partial inductance • proposed by A. Ruehli • The return path is assumed at infinite for each conductor segment • It can be directly appliable to circuit simulator like SPICE

Partial Inductance (cont.) Loop inductance between loop i and j is (assume loop i consists of K segments and loop j does M segments) So, loop inductance is

Partial Inductance (cont.) • Definition of partial inductance • The sign of partial inductance is not considered • So, partial inductance is solely dependent of conductor geometry • Sign rule for partial inductance where, Skm = +1 or –1 • The sign depends on the direction of current flow in the conductors

Outline Capacitance Extraction Introduction Table based method Formula based method Reading assignment Inductance Extraction Introduction Table based method Formula based method Reading assignment RLC circuit model generation Reading assignment Finite element method (FEM) based Extraction Overview of FEM FEM based Extraction Flow Reading assignment Homework

Inductance Extraction from Geometries • Numerical method based on Maxwell’s equations • Accurate, but way too slow for iterative physical design and verification • Efficient yet accurate models • Coplanar bus structure [He-Chang-Shen-et al, CICC’99] • Strip-lines and micro-strip bus lines [Chang-Shen-He-et al, DATE’2K] • Used in HP for state-of-the-art CPU design

1.73 1.15 0.53 1.15 1.94 1.24 0.53 1.24 1.92 Assume edge traces are AC-grounded • leads to 3x3 loop inductance matrix Inductance has a long range effect • non-negligible coupling between t1 and t3, even with t2 between them It is not sufficient to consider only a single net Loop Inductance for N Traces Tw TwL TwR Tw Tw Ts Ts TsL TsR t1 t2 t3 tR tL

Table in Brute-Force Way is Expensive Tw TwL TwR Tw Tw 1.73 1.15 0.53 1.15 1.94 1.24 0.53 1.24 1.92 Ts Ts TsL TsR t1 t2 t3 tR tL • Self inductance has nine dimensions: • (n, length, location,TwL,TsL,Tw,Ts,TwR,TsR) • Mutual inductance has ten dimensions: • (n, length, location1, location2,TwL,TsL,Tw,Ts,TwR,TsR) • Length is needed because inductance is not linearly scalable

Partial Inductance for N Traces Tw TwL TwR Tw Tw 6.17 5.43 5.12 4.89 4.66 5.43 6.79 6.10 5.48 5.04 5.12 6.10 6.79 6.10 5.33 4.89 5.48 6.10 6.79 5.77 4.66 5.04 5.33 5.77 6.50 Ts Ts TsL TsR t1 t2 t3 tR tL • Treat edge traces same as inner traces • lead to 5x5 partial inductance table • Partial inductance model is more accurate compared to loop inductance model • Without pre-setting current return loop

6.17 5.43 5.12 4.89 4.66 5.43 6.79 6.10 5.48 5.04 5.12 6.10 6.79 6.10 5.33 4.89 5.48 6.10 6.79 5.77 4.66 5.04 5.33 5.77 6.50 6.50 Propose and validate five foundations Foundation I: The self inductance under the PEEC model for a trace depends only on the trace itself (w/ skin effect for a given frequency). TwL Tw TwR Tw Tw Ts Ts TsL TsR t1 t2 t3 tR tL

6.17 5.43 5.12 4.89 4.66 5.43 6.79 6.10 5.48 5.04 5.12 6.10 6.79 6.10 5.33 4.89 5.48 6.10 6.79 5.77 4.66 5.04 5.33 5.77 6.50 6.17 4.66 4.66 6.50 Inductance – Table based method Foundation II: The mutual inductance under the PEEC model for two traces depends only on the traces themselves (w/ skin effect for given frequency). Tw TwL TwR Tw Tw Ts Ts TsL TsR t1 t2 t3 tR tL

Inductance – Table based method Foundation III: The self loop inductance for a trace on top of a ground plane depends only on the trace itself (its length, width, and thickness) TwL Tw TwR Tw Tw 4.8 2.5 1.3 0.7 0.14 2.5 5.5 2.9 1.5 0.7 1.3 2.9 5.7 2.9 1.3 0.7 1.5 2.9 2.5 2.5 0.14 0.7 1.3 2.5 4.8 Ts Ts TsL TsR t1 t2 t3 tR tL 4.8 tR

Inductance – Table based method Foundation IV: The mutual loop inductance for two traces on top of a ground plane depends only on the two traces themselves (their lengths, widths, and thickness) TwL Tw TwR Tw Tw 4.8 2.5 1.3 0.7 0.14 2.5 5.5 2.9 1.5 0.7 1.3 2.9 5.7 2.9 1.3 0.7 1.5 2.9 2.5 2.5 0.14 0.7 1.3 2.5 4.8 Ts Ts TsL TsR t1 t2 t3 tR tL 0.14 4.8 tL tR 4.8 0.14

Validation and Implication of Foundations • Foundations I and II can be validated theoretically • Foundations III and IV were verified experimentally • Problem size of inductance extraction can be greatly reduced w/o loss of accuracy • Solve 1-trace problem for self inductance • Reduce 9-D table to 2-D table • Solve 2-trace problem for mutual inductance • Reduce 10-D table to 3-D table

Outline Capacitance Extraction Introduction Table based method Formula based method Reading assignment Inductance Extraction Introduction Table based method Formula based method Reading assignment RLC circuit model generation Reading assignment Finite element method (FEM) based Extraction Overview of FEM FEM based Extraction Flow Reading assignment Homework

x z Conductor 1 Conductor 2 Dz l T Dx W y Dy Inductance – formula based method • Inductance Extraction from Geometries • Conductor Geometry • Inductance Formulae • Self Inductance : Grover(1962), Hoer(1965), Ruehli(1972), FastHenry(1994) • Mutual Inductance : Grover(1962), Hoer(FastHenry)(1965), Ruehli(1972) (a) Single Conductor (b) Two Parallel Conductors

Self Inductance – Grover’s formula l T W • For single straight wire: • length: l • width: W • thickness: T • With the filament approximation (W, T<< l), the self-inductance Lself-L can be written as • μ is the permeability of conductor. 49

Mutual Inductance – Grover’s Formula D Conductor 1 Conductor 2 l T W • For two parallel and aligned wires of the same width W, thickness T, length l, and center-to-center distance D. • With the filament approximation (W, T<< l), the mutual-inductance Lmutual-L can be written as 50