各種波形フォーマット変換 / タイミングダイアグラム描画 テストベンチ生成

各種波形フォーマット変換 / タイミングダイアグラム描画 テストベンチ生成. SynaptiCAD 社概要 - W ho is SynaptiCAD Inc. ?. 創立 1992年 あまり手をつけられていない、タイミング波形編集/解析の周辺に特化して、質の高い安価なツールを供給することにビジネスチャンスを見出し、タイミング波形に関するセンター・ツールを目指して。 創立者 Mr.Daniel Notestein/ Ms.Donna Mitchell 場所 Blacksburg, VA, USA- Virginia Tech の町 社員数 22名(エンジニア15名).

各種波形フォーマット変換 / タイミングダイアグラム描画 テストベンチ生成

E N D

Presentation Transcript

各種波形フォーマット変換 / タイミングダイアグラム描画 • テストベンチ生成

SynaptiCAD社概要 - Who is SynaptiCAD Inc. ? • 創立 1992年 • あまり手をつけられていない、タイミング波形編集/解析の周辺に特化して、質の高い安価なツールを供給することにビジネスチャンスを見出し、タイミング波形に関するセンター・ツールを目指して。 • 創立者Mr.Daniel Notestein/ Ms.Donna Mitchell • 場所Blacksburg, VA, USA- Virginia Tech の町 • 社員数 22名(エンジニア15名)

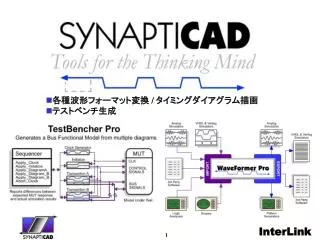

SynaptiCADのツールについて ■SnaptiCAD社は、波形変換/タイミングダイアグラムエディタを中心に 下記のようなツールを提供しております。 • GigaWave Viewer–VCD/TDML 波形ビューワ • Timing Diagrammer Pro–タイミングダイアグラムエディタ • WaveFormer Pro–タイミングダイアグラムエディタ+波形変換 • DataSheet Pro–タイミングダイアグラム+波形変換を含む ドキュメント作成支援ツール • VeriLogger Extreme–グラフィカルな入力によるテストベクタ 生成機能付きVerilogシミュレータ • TestBencher Pro–グラフィカルな入力によるテストベンチ 生成ツール

SynaptiCADツール主な機能 • タイミングダイアグラムの描画/タイミング解析・ マウスクリック/ドラッグ&ドロップ ベースによる波形描画・ 波形上でのdelay/Setup/Holdよるタイミング解析 ・ 式による、波形入力や値の入力-ランダムな値も入力可・ 波形描画画面でドキュメント作成支援 グリッドライン, タイムコンプレスマーカ・ Boolean Equationによる信号定義 • 各種波形フォーマットの変換 ・ロジアナで吸い上げた実機データをシミュレータに利用・タイミングダイアグラムから、HDLスティミュラスを生成・シミュレータのデータ(vcdファイル)をパタンジェネレータで実機環境で利用

SynaptiCADツール主な機能 • バスファンクション・モデルによる テストベンチの生成(TBP機能)・グラフィカルなタイミングダイアグラムから バスファンクション・モデルを生成(BFM:トランザクション+駆動シーケンス) =複雑なトランザクションを視覚的に編集し維持管理できる・言語に非依存なタイミングダイアグラムから テストベンチを生成

タイミングダイアグラム描画機能 • マウスクリック/ドラッグ&ドロップ ベースによる直感的な操作で、 タイミングダイアグラム描画をすることが可能です。 • 波形上でのdelay/Setup/Holdよるタイミング解析、 式による波形入力、Boolean 式による信号定義も可能 • ステートボタンで描画したい波形の種類を決定、時間軸でマウスクリックすることにより波形を描画。 • Boolean 式からの波形生成例(SIG2は、SIG0とSIG1のANDを とったもの) • delayを与えた例 • 式からの波形入力例

インポート機能 Import可能なファイル・フォーマット • Timing Project(syncad) • SynaptiCAD wave format • VCD • Spice CSDF/tr0 Format • Synopsys TimeMill • TimingDesigner • Tektronix Logic Analyzer • Test Vector Spreadsheet • Agilrent Logic Analyzer • その他

エクスポート機能 Export可能なファイル・フォーマット • Timing Project(syncad) • SynaptiCAD wave format • VCD • VHDL • Verilog • Spice source • Hspice source • Pspice digital • HSim Spice • Abel stimulus • Tektronix Test Vector • Agilent Pattern Generator • PI-2005 Pattern Generator • STIL Test Vectors • その他

バスファンクション・モデルによるテストベンチ生成(TBP)バスファンクション・モデルによるテストベンチ生成(TBP) MUTとTBの「ヤリトリ」を バス・トランザクション要素とその駆動シーケンスに「分解」 BFM = トランザクション+駆動シーケンス MUT( HDL~*.vhd/*.v )+トランザクション(*.tim)+テストベンチ・スクリプト =>テストベンチ(HDL~*.vhd/*.v)

バスファンクション・モデルによるテストベンチ生成(TBP)バスファンクション・モデルによるテストベンチ生成(TBP) トランザクション 各トランザクションは、再利用可能な波形タイミングモデルとして記述=> *.btim ファイル addr、dataのパラメタライズ ・パラメータ化したステート 変数を使用したタイミング値 ・ドライブ信号と期待値信号を カラー表示で区別 ・サンプル値に対する if~then~elseの検証

バスファンクション・モデルによるテストベンチ生成(TBP)バスファンクション・モデルによるテストベンチ生成(TBP) トップレベル・モジュールにおいて、 トランザクションのシーケンスを定義 駆動シーケンス 定義した 「パラメタライズド」トランザクションを 駆動するシーケンスプログラムを 「擬似コード」で記述 =>テストベンチ・スクリプト 観測、照合の記述も含む • トランザクションのコール • Apply_tbread(…)など • トップレベルにおけるさまざまなプロセスの定義 • for loopなど

計測器データのインポート/エクスポート 実機動作検証 - シミュレータの入力波形を実機への入力信号に、 出力波形は期待値としてサンプリングした信号と比較 シミュレーション結果と実機データをマージして同一信号名を自動比較し差異をハイライト WaveFormer Proで入力信号を変換 シミュレーション結果 (VHDL / Verilog・・) パタン・ジェネレータ 実チップ(またはボード) マージ マージ WaveFormerへ 比較 実機からのデータをWaveFormer Proへ読み込み ロジック・アナライザ

波形からVerilogパタ-ンの生成 波形 Verilog 。。。(略)。。。 module stimulus(CLK0, SIG0, SIG1, SIG2); output CLK0; output SIG0; output [3:0] SIG1; output SIG2; reg SIG0_driver; 。。。(略)。。。 。。。(略)。。。 begin #50.0; SIG2_driver <= 1'b0; #50.0; SIG0_driver <= 1'b1; SIG1_driver <= 4'h8; 。。。(略)。。。

InterLink 有限会社インターリンク 231-0023 横浜市中区山下町 252 グランベル横浜9FTEL:045-663-5940 FAX:045-663-5945 ilink_sales@ilink.co.jp http://www.ilink.co.jp *本資料の無断複製・転載を禁じます。