Circuit Analysis: Voltage, Current, and Capacitance Computation

This document encapsulates a series of circuit analysis problems focusing on voltage (Vo) across a supernode, current relationships, and equivalent capacitance (Ceq) in complex configurations. It explores the use of Kirchhoff's laws (KCL and KVL), analyzing voltages in specific nodes with resistances and voltage sources. Key questions include finding the voltage across capacitors and calculating initial currents under defined conditions. This comprehensive study aids in understanding fundamental circuit behavior in electrical engineering.

Circuit Analysis: Voltage, Current, and Capacitance Computation

E N D

Presentation Transcript

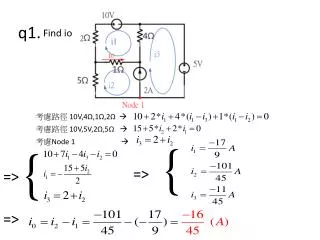

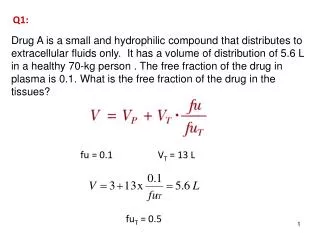

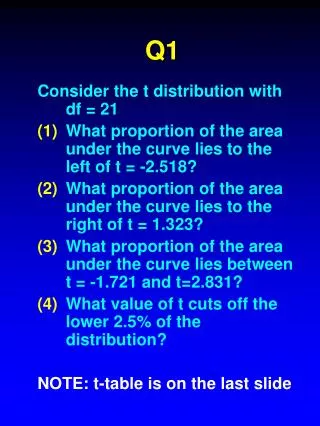

q1. Find io 考慮路徑 10V,4Ω,1Ω,2Ω 考慮路徑 10V,5V,2Ω,5Ω { 考慮Node 1 { => => =>

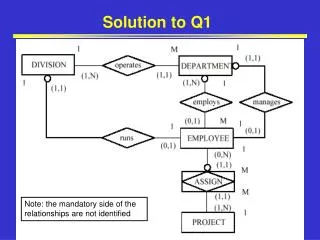

q2. Find Vo Supernode : v1,3vo,v2 2=i1+i2+i3+i4 => , => => =>

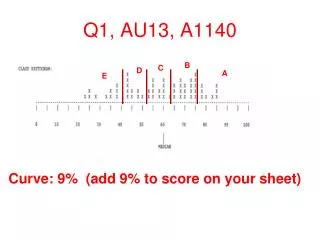

1. 2.

3. 4.

q5. Ceq =C5並{C4 串 [C3 並 ( C2串 C1 )]} (a)find Ceq C1 = C2=C3 = C4 = C5 = C (b) Assume that the initional conditions are zero. If a source of Vs is connected to terminal a and b, what is the voltage across C1 capacitor? =>

Given that V(t) = 10e-3t mV for t > 0 and i1(0)=-10 mA, find q6. i2(0) i2(0) * L2 = i1(0) * L1= -10m *20m => i2(0) = (b) i1(t) (c) i2(t)